FMステレオ復調を実装

やっとFMステレオ復調処理を実装しました。処理としては、 ディジタルFMステレオ・チューナの製作 ―― 雑誌の付属基板でここまでできる(ステレオ復調回路)にある通りです。

今回の実装について以下に説明しますが、勘違いしている可能性もありますので、 ご自分で確認してください。

DDSのIPを置いて、位相を可変とした19kHzのsin, cos信号を生成します。 cos信号とFM復調信号を掛け算し、その結果をLPFに通します。 LPFは、CICでfsを1/20にして(fs=500kHzからfs=25kHzに)、続いてFIRでfc=1kHzのフィルタを掛けました。 そして、この値に応じて、DDSで発振する19kHz信号の位相を進めたり遅らせたりします。

具体的には、パイロット信号をsin 19kHzとすると、三角関数の公式により、 sin x * cos y = 1/2 * {sin(x-y)+sin(x+y)} です。今回は、sin 19kHz * cos 19kHz = 1/2 * {sin(0) + sin(38kHz)} となります。LPFを通すことでsin(38kHz)は0になりますので、sin(0)だけが残ります。 つまり、パイロット信号と同調したcos信号が得られれば、sin(0)=0となります。 ただし、sinが0となるのは、0(x=yのとき)とπ(x=y+πのとき)がありますが、今回は0になるようにします。 それで、sinが正であれば、cosの位相(y)を増やし、sinが負であれば、 cosの位相を減らして、sin(x-y)のx-yが0となるように制御しました。

このようにsinのパイロット信号に対してcosの信号が得られたら、倍角の公式 sin 2x = 2 sin x * cos x により、DDSのsin, cos信号を掛け算することで、パイロット信号に同期した38kHzの信号が得られることになります。

あとは、この38kHzの信号をFM復調信号に掛け算し、LPFを通すことでL-Rの信号が得られます。

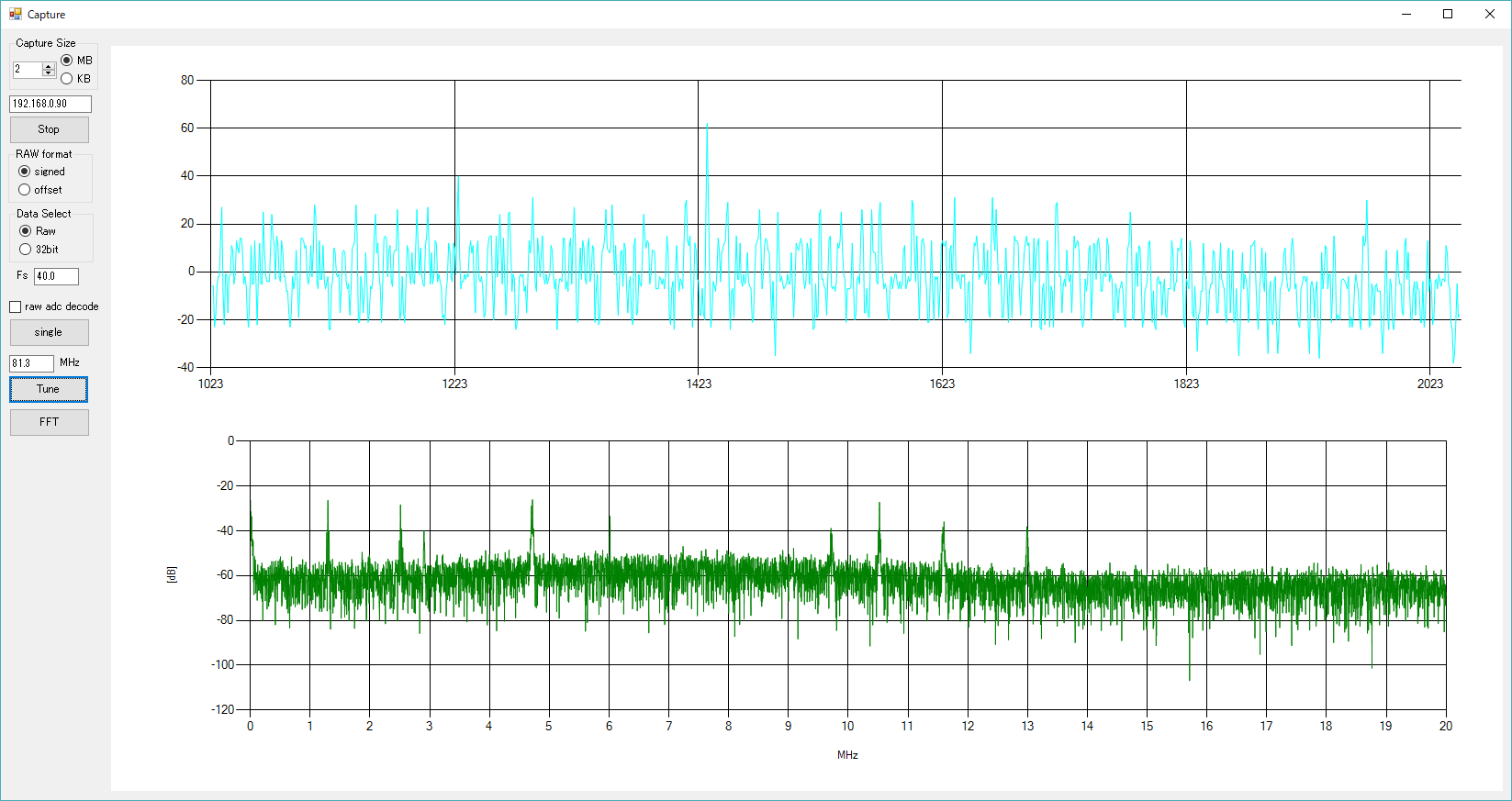

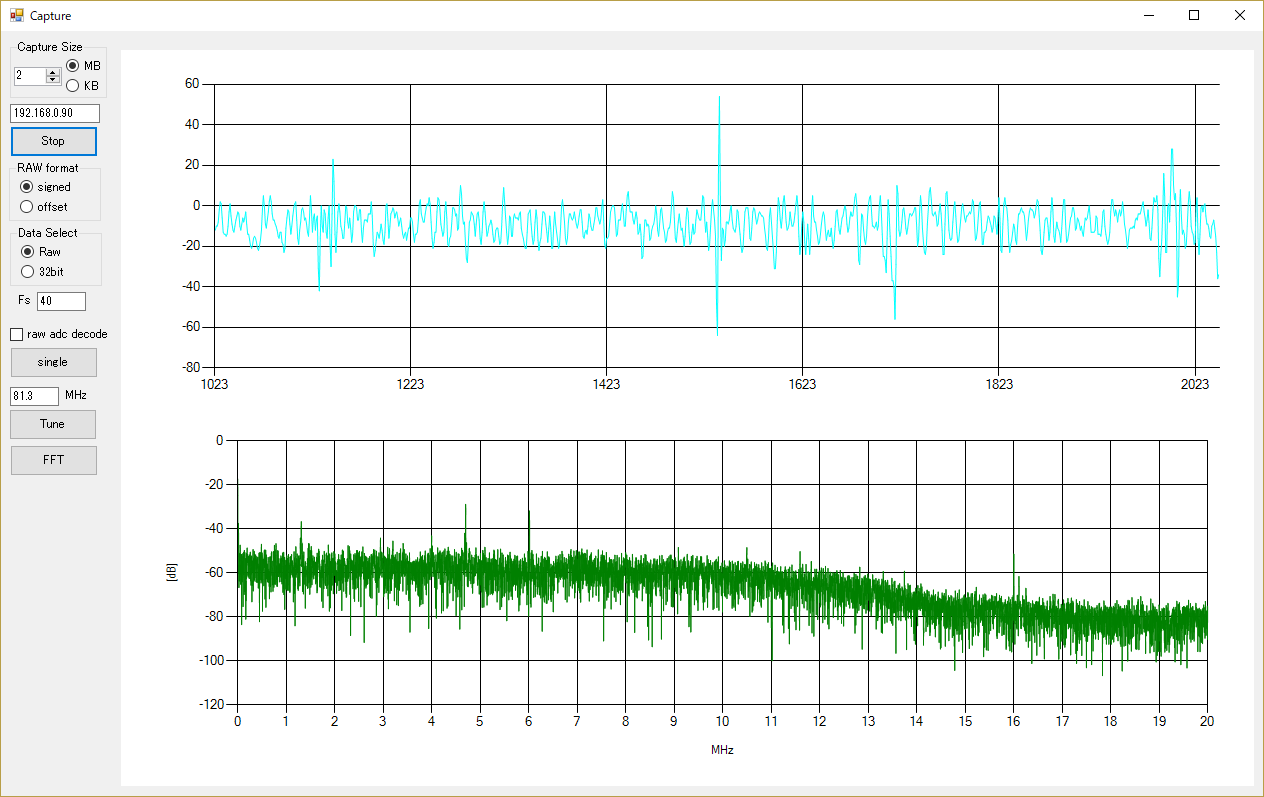

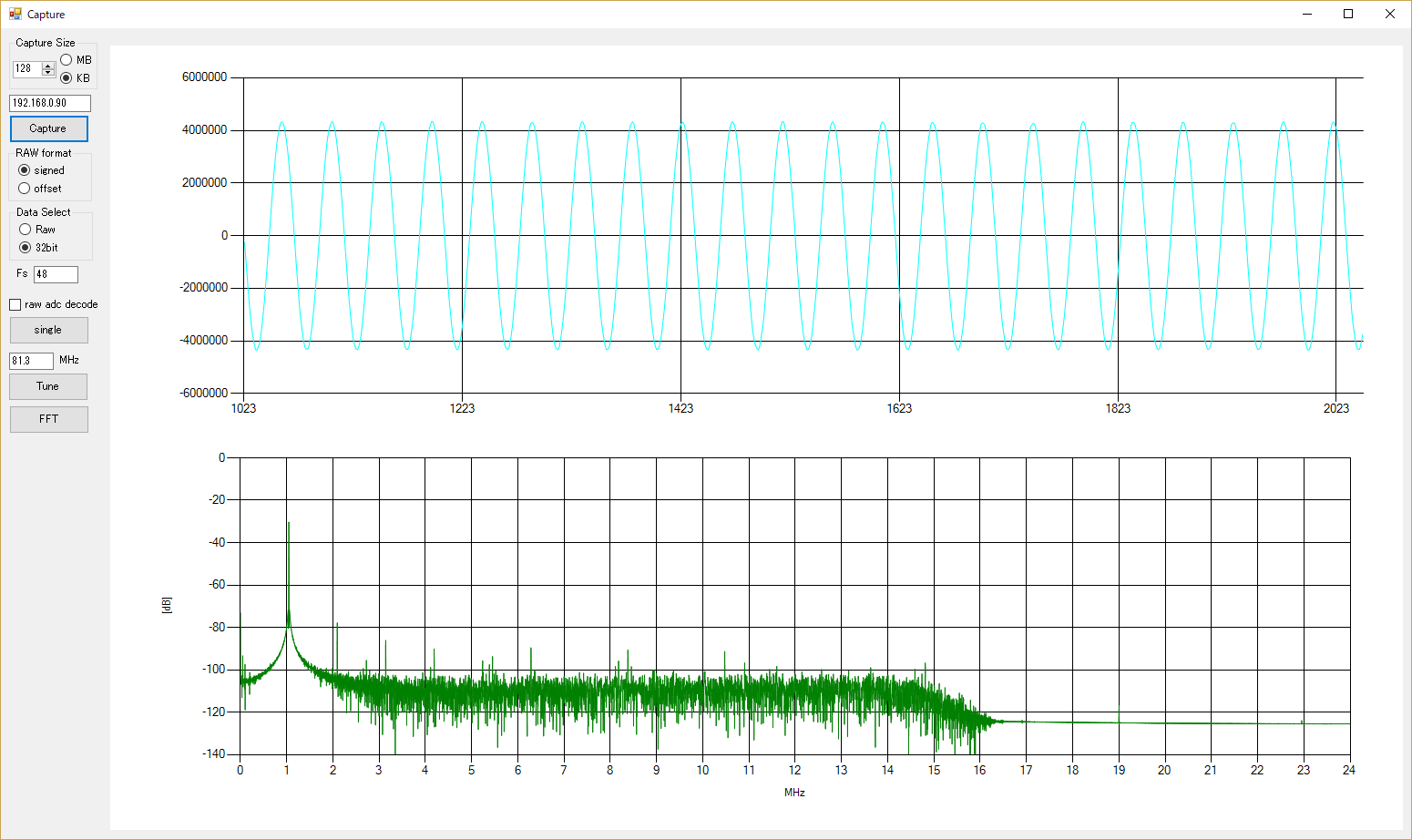

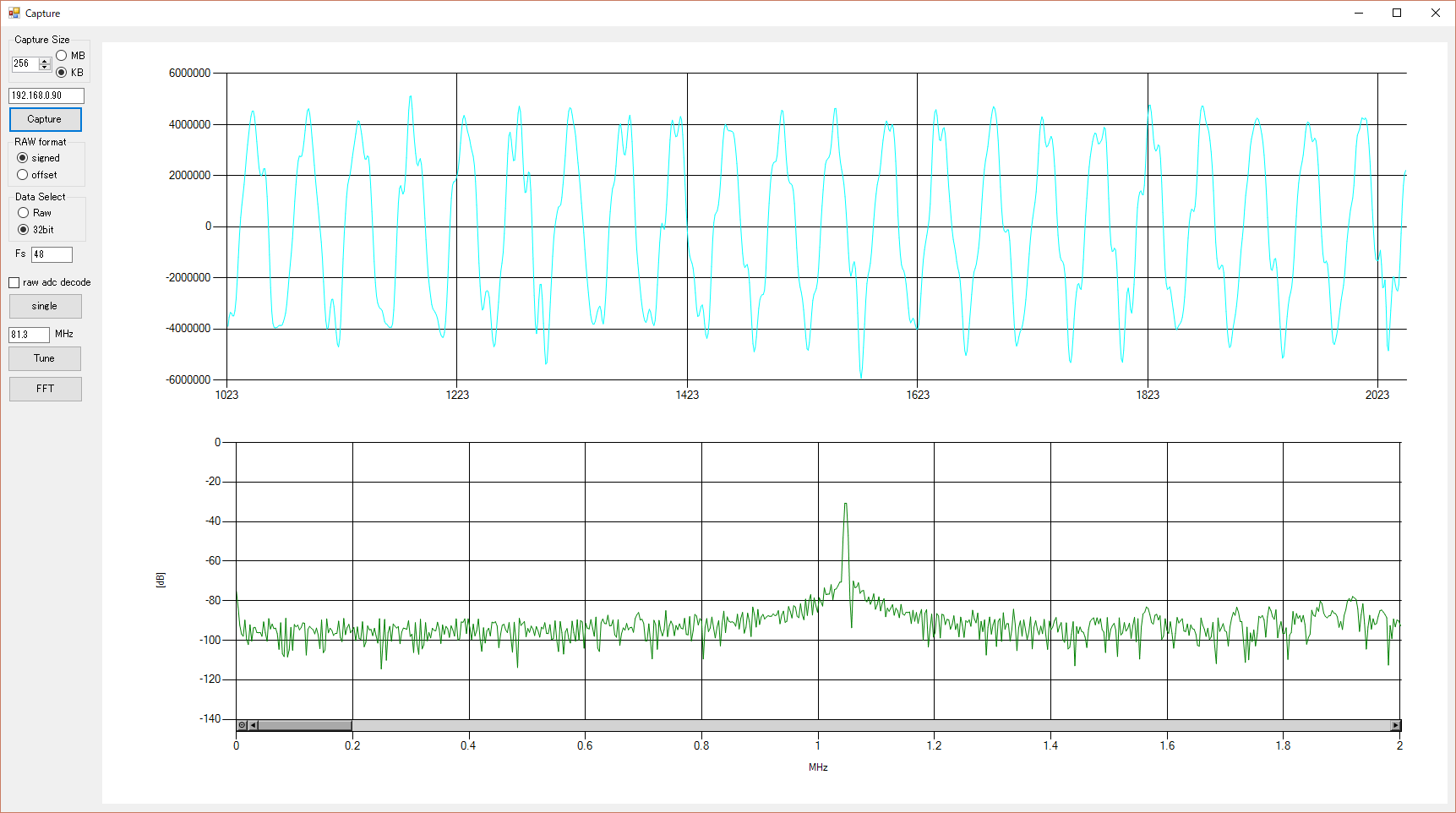

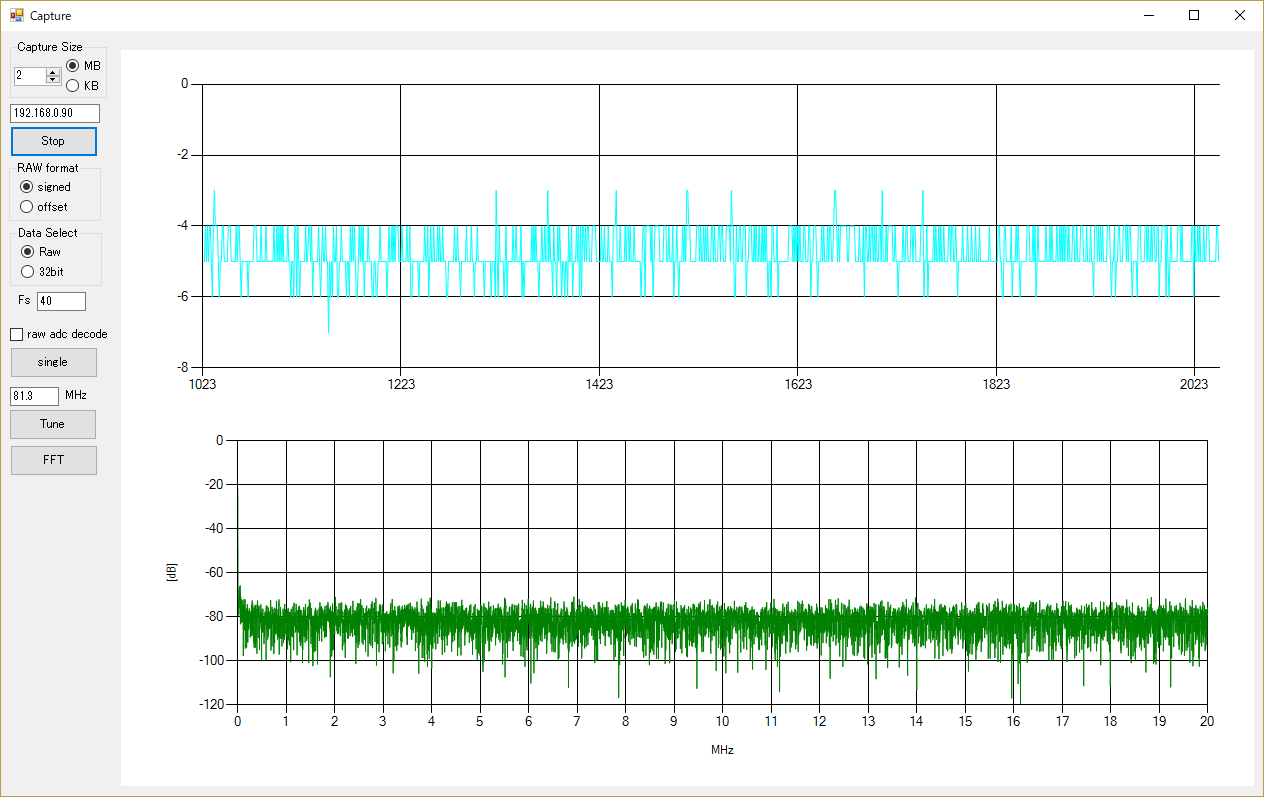

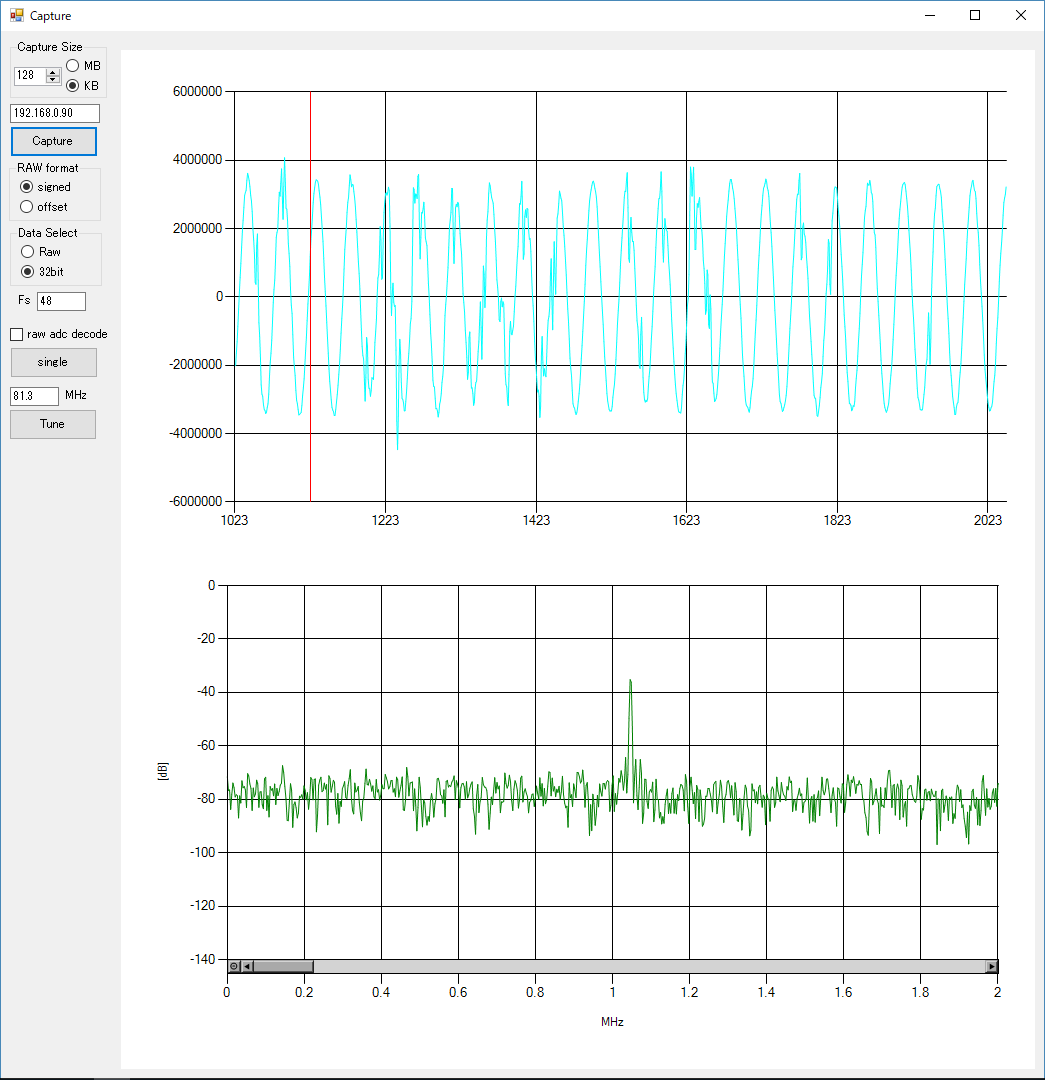

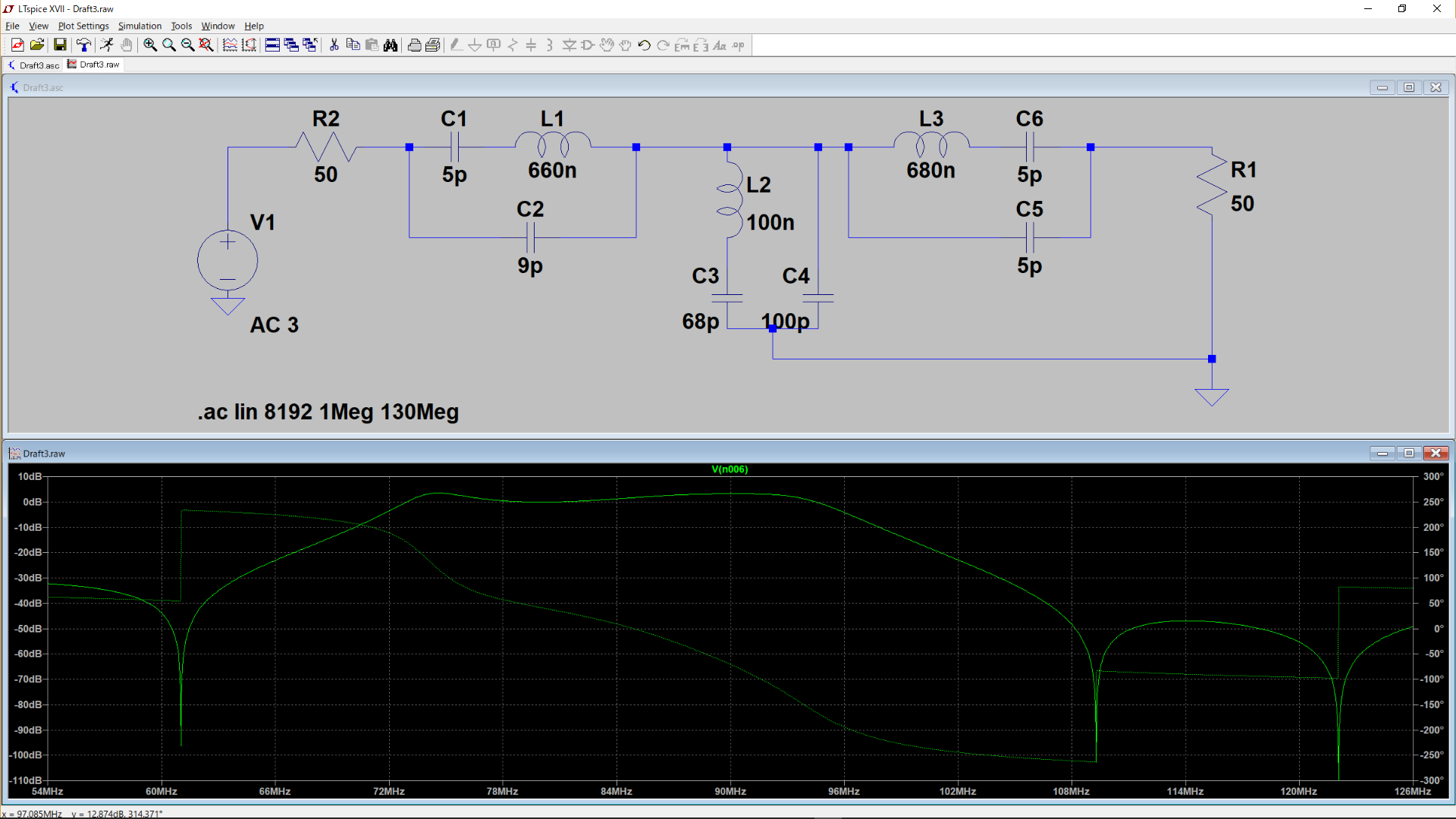

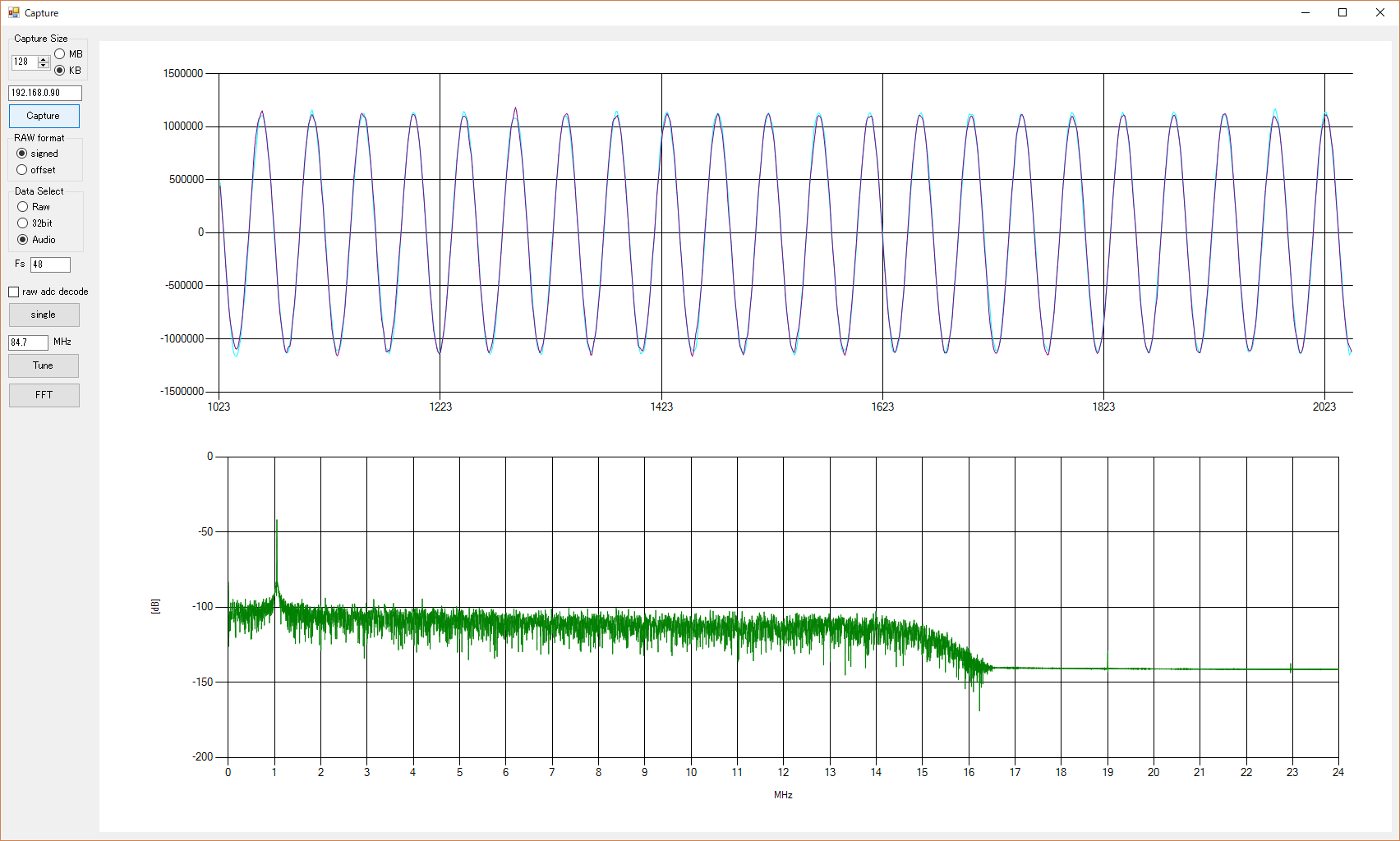

この状態で時報信号をキャプチャしたものが次になります。

ちょっと分かりにくいですが、上側のグラフは、左右の音声を別々の色で描画しています。 時報信号だと恐らく左右同じ音声信号になってしまっているので、ほとんど重なってしまい、 分かりにくいです。

実際に聞いてみて、確かにこれまでより奥行きが感じられるようになりました。 ただ、この実装がどれほど正しいかは、上のグラフだけでは分かりません。 本来であれば左だけ、右だけの音声を復調してみて、それが正確に再生されるか確認する必要があります。 ただ、手ごろなFMトランスミッタを持ち合わせていないので、このような確認まではできていません。