FM BPFのシミュレーション(2)

前回に引き続き、トラ技の記事の回路をシミュレーションしてみます。 今回はLNAの電源に使用されているフィルタ部について行いました。

記事で使用しているPSA4-5043は入手できなくなっている(?)ようなので、PSA4-5043+を使用するつもりです。 このチップは、RF出力と同じピンから、チップの電源を供給します。デジタルだと考えられないですが、 結局電圧のバイアスをかけるだけであり、RF信号はいずれにせよ後段でAC結合でバイアスは取り除きますので、 問題にならないのだと思います。

でも、この端子から電源を入れるとなると、こちらにノイズが混入しては元も子もありません。 電源部のためのフィルタ回路が組まれています。

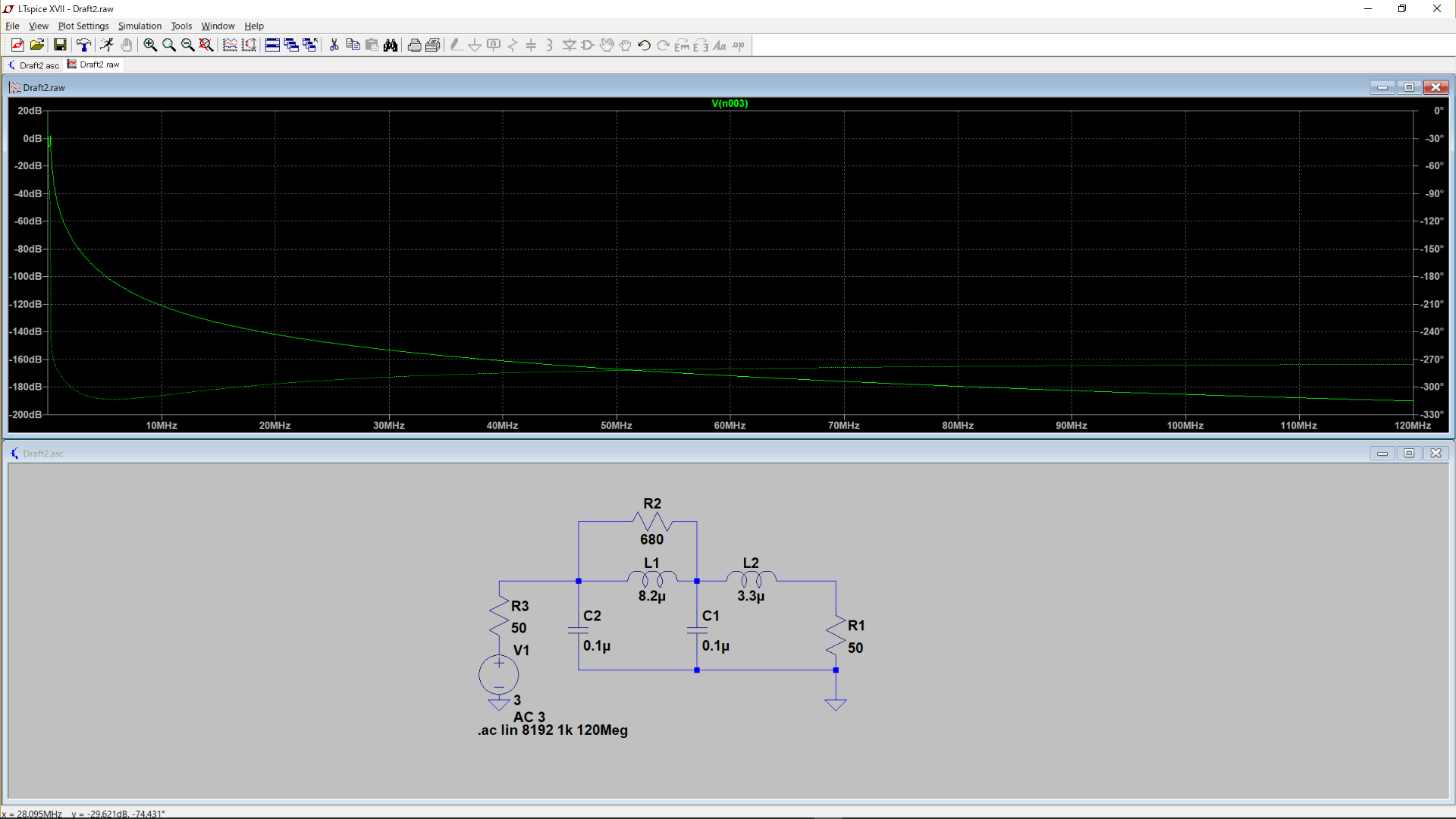

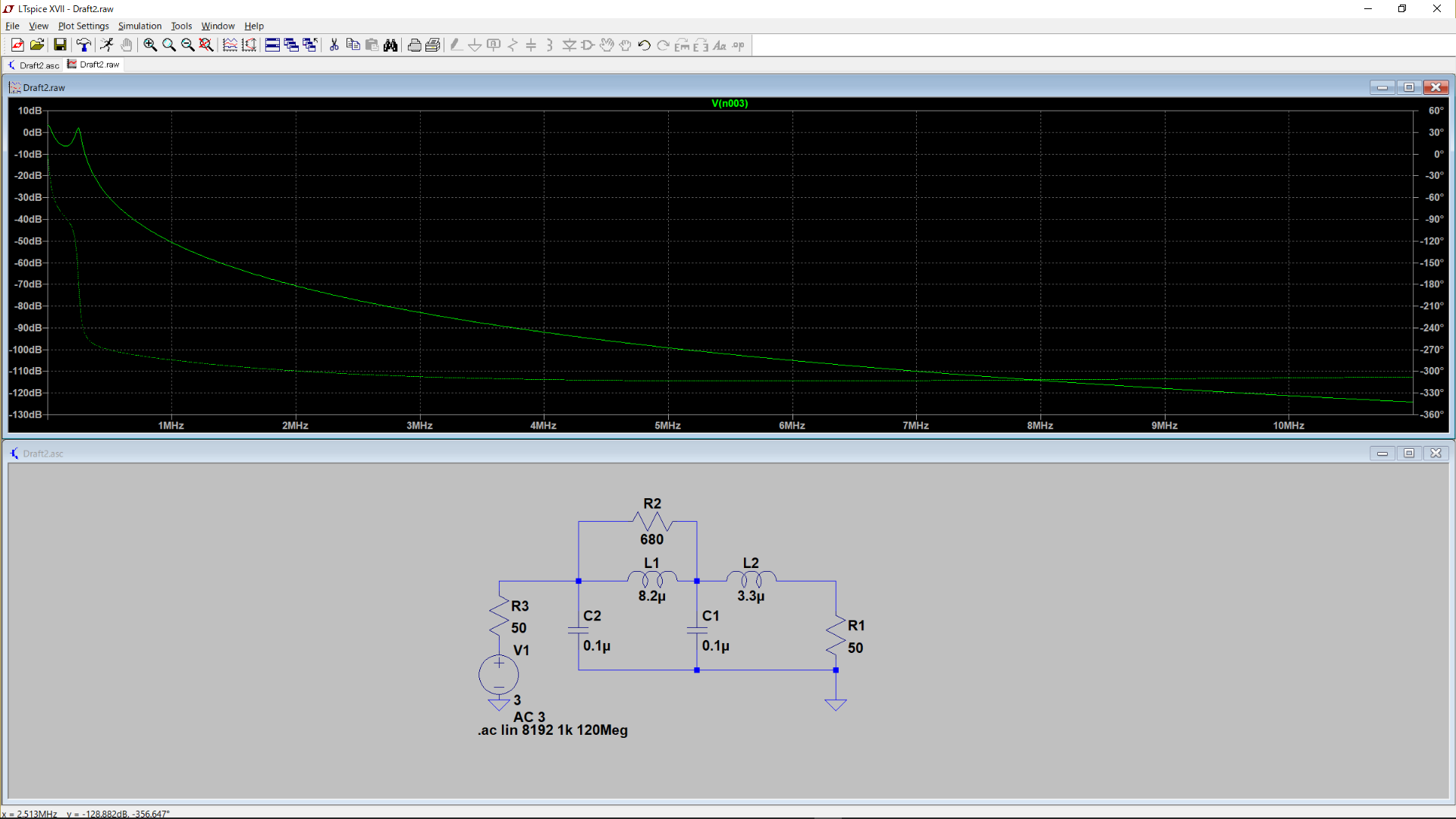

シミュレーション結果は次のようになりました。

まずは、DCから120MHz全体のゲインの様子です。

次に、DCから11MHzまでを拡大してみます。

1MHzを越えると-50dB以上減衰できているようです。低周波数の領域についてはそれほど減衰していません。 こちらについてはLDOで落とすことも考えられますが、果たして必要なのか? この領域であれば、 アナログにノイズが混入しても、デジタルミキサで周波数を移動してLPFをした時点で取り除けるような気もします。

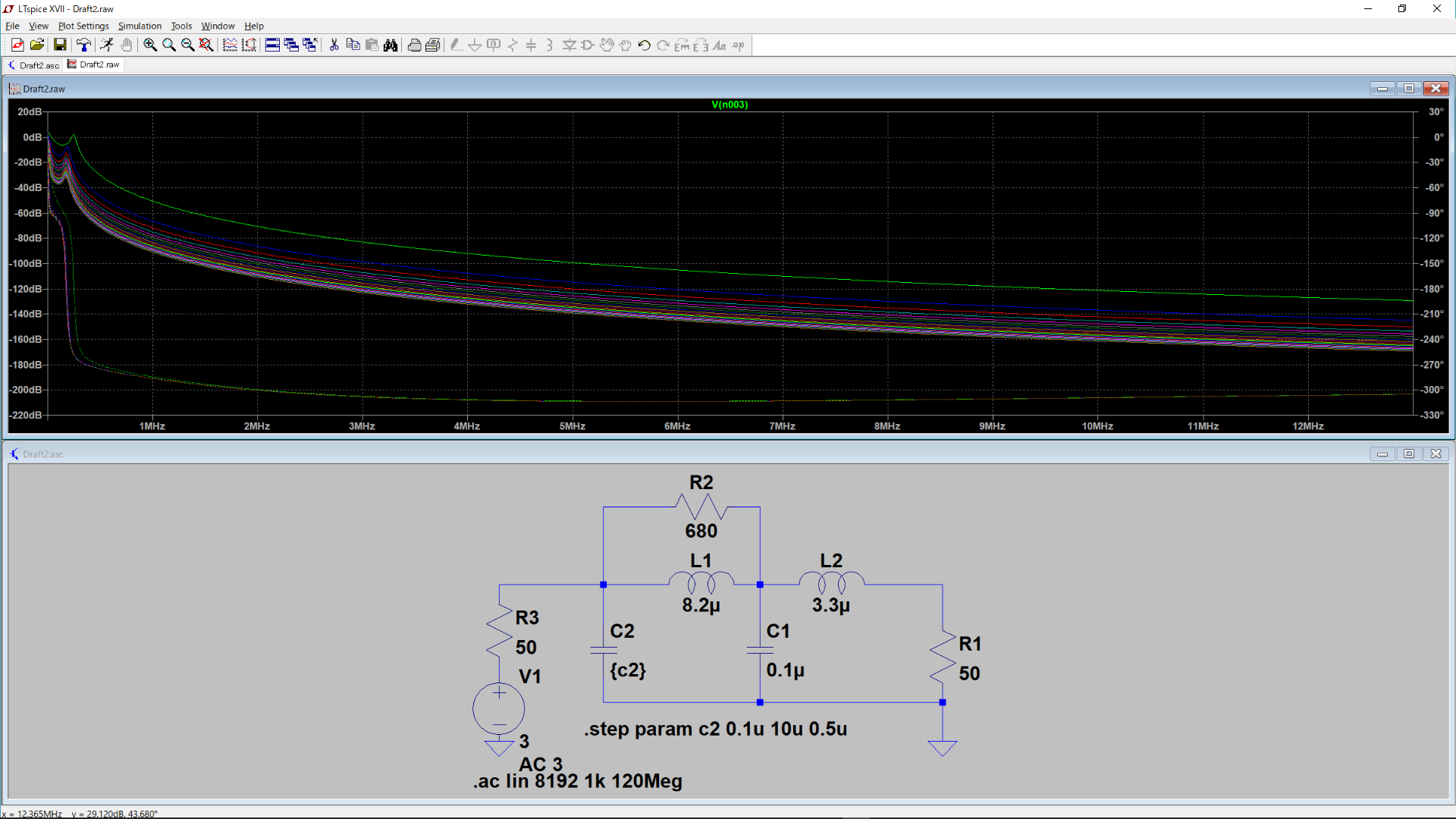

**2017/9/9追記:**次は、入力側のキャパシタの値を0.1uFから10uFまで変化させたときのシミュレーションです。 容量が大きくなるほど減衰量が大きくなっていることが分かります。 製作した基板に使用した0603サイズでも10uF程度のセラコンは入手できそうでした。

下記も参考になりそうなので、後々読んでみたいと思います: