先日注文していたZ-turn Boardが到着しました。動作確認をひとまず行いました。

東芝の4GBのMicroSDカードが付属しているので、それを装着して電源を入れると、

Linuxが起動します。HDMIモニタに映像も出力されます。

USB_UARTで電源供給とターミナル接続ができますが、USBコネクタがMini-Bタイプでした。

最近珍しいですね。

いきなりdmesgで恐らくSDカードでのファイルシステムエラーが出ていますが、

ボードとしての機能は問題なさそうです。

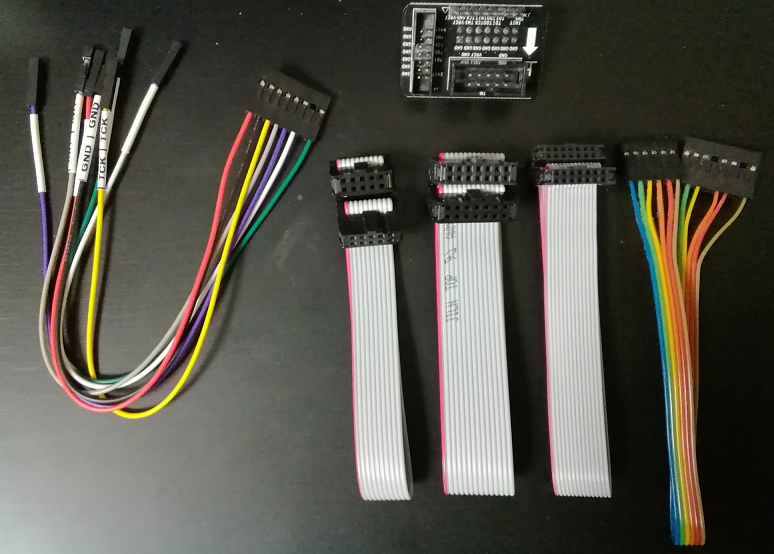

先行して到着していたXilinx互換ケーブルで認識できることも確認しました。

ちなみに、PayPal経由での請求は、$144が16437円でした。レートにすると114.16円くらい。最近変動が激しいですが、

1%くらいしか手数料は乗っていないのではないかと思われます。

freeroot@localhost:~# free

total used free shared buffers cached

Mem: 771712 319528 452184 0 18980 124896

-/+ buffers/cache: 175652 596060

Swap: 0 0 0

root@localhost:~# dmesg

Dentry cache hash table entries: 131072 (order: 7, 524288 bytes)

Inode-cache hash table entries: 65536 (order: 6, 262144 bytes)

Memory: 640440K/786432K available (5236K kernel code, 261K rwdata, 1616K rodata, 200K init, 207K bss, 145992K reserved, 8192K highmem)

Virtual kernel memory layout:

vector : 0xffff0000 - 0xffff1000 ( 4 kB)

fixmap : 0xfff00000 - 0xfffe0000 ( 896 kB)

vmalloc : 0xf0000000 - 0xff000000 ( 240 MB)

lowmem : 0xc0000000 - 0xef800000 ( 760 MB)

pkmap : 0xbfe00000 - 0xc0000000 ( 2 MB)

modules : 0xbf000000 - 0xbfe00000 ( 14 MB)

.text : 0xc0008000 - 0xc06b9588 (6854 kB)

.init : 0xc06ba000 - 0xc06ec380 ( 201 kB)

.data : 0xc06ee000 - 0xc072f7a0 ( 262 kB)

.bss : 0xc072f7ac - 0xc07634a4 ( 208 kB)

Preemptible hierarchical RCU implementation.

Dump stacks of tasks blocking RCU-preempt GP.

RCU restricting CPUs from NR_CPUS=4 to nr_cpu_ids=2.

RCU: Adjusting geometry for rcu_fanout_leaf=16, nr_cpu_ids=2

NR_IRQS:16 nr_irqs:16 16

slcr mapped to f0002000

zynq_clock_init: clkc starts at f0002100

Zynq clock init

sched_clock: 16 bits at 54kHz, resolution 18432ns, wraps every 1207951633ns

timer #0 at f0004000, irq=43

Console: colour dummy device 80x30

Calibrating delay loop... 1332.01 BogoMIPS (lpj=6660096)

pid_max: default: 32768 minimum: 301

Mount-cache hash table entries: 2048 (order: 1, 8192 bytes)

Mountpoint-cache hash table entries: 2048 (order: 1, 8192 bytes)

CPU: Testing write buffer coherency: ok

CPU0: thread -1, cpu 0, socket 0, mpidr 80000000

Setting up static identity map for 0x4f15f8 - 0x4f1650

L310 cache controller enabled

l2x0: 8 ways, CACHE_ID 0x410000c8, AUX_CTRL 0x72760000, Cache size: 512 kB

CPU1: Booted secondary processor

CPU1: thread -1, cpu 1, socket 0, mpidr 80000001

Brought up 2 CPUs

SMP: Total of 2 processors activated.

CPU: All CPU(s) started in SVC mode.

devtmpfs: initialized

VFP support v0.3: implementor 41 architecture 3 part 30 variant 9 rev 4

regulator-dummy: no parameters

NET: Registered protocol family 16

DMA: preallocated 256 KiB pool for atomic coherent allocations

cpuidle: using governor ladder

cpuidle: using governor menu

zynq device is 7z020

hw-breakpoint: found 5 (+1 reserved) breakpoint and 1 watchpoint registers.

hw-breakpoint: maximum watchpoint size is 4 bytes.

zynq-ocm f800c000.ocmc: ZYNQ OCM pool: 256 KiB @ 0xf0080000

VCCPINT: 1000 mV

vgaarb: loaded

SCSI subsystem initialized

usbcore: registered new interface driver usbfs

usbcore: registered new interface driver hub

usbcore: registered new device driver usb

media: Linux media interface: v0.10

Linux video capture interface: v2.00

pps_core: LinuxPPS API ver. 1 registered

pps_core: Software ver. 5.3.6 - Copyright 2005-2007 Rodolfo Giometti <giometti@linux.it>

PTP clock support registered

EDAC MC: Ver: 3.0.0

Advanced Linux Sound Architecture Driver Initialized.

cfg80211: Calling CRDA to update world regulatory domain

Switched to clocksource ttc_clocksource

NET: Registered protocol family 2

TCP established hash table entries: 8192 (order: 3, 32768 bytes)

TCP bind hash table entries: 8192 (order: 4, 65536 bytes)

TCP: Hash tables configured (established 8192 bind 8192)

TCP: reno registered

UDP hash table entries: 512 (order: 2, 16384 bytes)

UDP-Lite hash table entries: 512 (order: 2, 16384 bytes)

NET: Registered protocol family 1

RPC: Registered named UNIX socket transport module.

RPC: Registered udp transport module.

RPC: Registered tcp transport module.

RPC: Registered tcp NFSv4.1 backchannel transport module.

PCI: CLS 0 bytes, default 64

hw perfevents: enabled with ARMv7 Cortex-A9 PMU driver, 7 counters available

futex hash table entries: 512 (order: 3, 32768 bytes)

bounce pool size: 64 pages

jffs2: version 2.2. (NAND) (SUMMARY) \xffffffc2\xffffffa9 2001-2006 Red Hat, Inc.

msgmni has been set to 1490

io scheduler noop registered

io scheduler deadline registered

io scheduler cfq registered (default)

dma-pl330 f8003000.dmac: Loaded driver for PL330 DMAC-2364208

dma-pl330 f8003000.dmac: DBUFF-128x8bytes Num_Chans-8 Num_Peri-4 Num_Events-16

e0000000.serial: ttyPS1 at MMIO 0xe0000000 (irq = 59, base_baud = 6249999) is a xuartps

e0001000.serial: ttyPS0 at MMIO 0xe0001000 (irq = 82, base_baud = 6249999) is a xuartps

console [ttyPS0] enabled

xdevcfg f8007000.devcfg: ioremap 0xf8007000 to f006a000

[drm] Initialized drm 1.1.0 20060810

brd: module loaded

loop: module loaded

m25p80 spi0.0: found s25fl129p1, expected n25q128

m25p80 spi0.0: s25fl129p1 (16384 Kbytes)

7 ofpart partitions found on MTD device spi0.0

Creating 7 MTD partitions on "spi0.0":

0x000000000000-0x000000080000 : "qspi-boot"

0x000000080000-0x0000000a0000 : "qspi-bootenv"

0x0000000a0000-0x000000500000 : "qspi-bitstream"

0x000000500000-0x000000980000 : "qspi-kernel"

0x000000980000-0x000000990000 : "qspi-devicetree"

0x000000990000-0x000000f90000 : "qspi-rootfs"

0x000000f90000-0x000001000000 : "data"

CAN device driver interface

libphy: MACB_mii_bus: probed

macb e000b000.ethernet eth0: Cadence GEM at 0xe000b000 irq 54 (00:0a:35:00:01:22)

macb e000b000.ethernet eth0: attached PHY driver [Generic PHY] (mii_bus:phy_addr=e000b000.etherne:03, irq=-1)

e1000e: Intel(R) PRO/1000 Network Driver - 2.3.2-k

e1000e: Copyright(c) 1999 - 2014 Intel Corporation.

PPP generic driver version 2.4.2

PPP BSD Compression module registered

PPP Deflate Compression module registered

usbcore: registered new interface driver rtl8192cu

ehci_hcd: USB 2.0 'Enhanced' Host Controller (EHCI) Driver

ehci-pci: EHCI PCI platform driver

ULPI transceiver vendor/product ID 0x0424/0x0007

Found SMSC USB3320 ULPI transceiver.

ULPI integrity check: passed.

zynq-ehci zynq-ehci.0: Xilinx Zynq USB EHCI Host Controller

zynq-ehci zynq-ehci.0: new USB bus registered, assigned bus number 1

zynq-ehci zynq-ehci.0: irq 53, io mem 0x00000000

zynq-ehci zynq-ehci.0: USB 2.0 started, EHCI 1.00

hub 1-0:1.0: USB hub found

hub 1-0:1.0: 1 port detected

usbcore: registered new interface driver usb-storage

usbcore: registered new interface driver usbserial

usbcore: registered new interface driver usbserial_generic

usbserial: USB Serial support registered for generic

usbcore: registered new interface driver option

usbserial: USB Serial support registered for GSM modem (1-port)

mousedev: PS/2 mouse device common for all mice

usbcore: registered new interface driver synaptics_usb

ft5x0x_ts_init successful

input: gpio-beep.3 as /devices/amba.1/gpio-beep.3/input/input0

i2c /dev entries driver

input: ADXL34x accelerometer as /devices/amba.1/e0004000.i2c/i2c-0/0-0053/input/input1

sii902x 0-003b: sii902x_probe

Sii902x: read id = 0xB0

-0x02-0x03

-0x00

myir_stlm75x_probe()

myir-stlm75x driver initialized successfully!

cdns-i2c e0004000.i2c: 400 kHz mmio e0004000 irq 57

cdns-wdt f8005000.watchdog: Xilinx Watchdog Timer at f007a000 with timeout 10s

zynq-edac f8006000.memory-controller: ecc not enabled

cpufreq: __cpufreq_add_dev: CPU0: Running at unlisted freq: 666666 KHz

cpufreq: __cpufreq_add_dev: CPU0: Unlisted initial frequency changed to: 666667 KHz

Xilinx Zynq CpuIdle Driver started

sdhci: Secure Digital Host Controller Interface driver

sdhci: Copyright(c) Pierre Ossman

sdhci-pltfm: SDHCI platform and OF driver helper

mmc0: no vqmmc regulator found

mmc0: no vmmc regulator found

mmc0: SDHCI controller on e0100000.sdhci [e0100000.sdhci] using ADMA

ledtrig-cpu: registered to indicate activity on CPUs

usbcore: registered new interface driver usbhid

usbhid: USB HID core driver

TCP: cubic registered

NET: Registered protocol family 17

can: controller area network core (rev 20120528 abi 9)

NET: Registered protocol family 29

can: raw protocol (rev 20120528)

can: broadcast manager protocol (rev 20120528 t)

can: netlink gateway (rev 20130117) max_hops=1

Registering SWP/SWPB emulation handler

mmc0: new high speed SDHC card at address 1234

mmcblk0: mmc0:1234 SA04G 3.63 GiB

mmcblk0: p1 p2

xylonfb video mode: 1280x720-32@60

Console: switching to colour frame buffer device 160x45

sii902x 0-003b: sii902x_fb_event event=0x5,

sii902x 0-003b: Sii902x: setup..

xylonfb 1 registered

sii902x 0-003b: sii902x_fb_event event=0x5,

xylonfb 0 registered

input: gpio-keys.4 as /devices/amba.1/gpio-keys.4/input/input2

drivers/rtc/hctosys.c: unable to open rtc device (rtc0)

sii902x 0-003b: det_worker

ALSA device list:

status: 0X1F, sii902x.retries: 2

sii902x 0-003b: EVENT=plugin

sii902x_poweron

No soundcards found.

sii902x 0-003b: exit det_worker

sii902x 0-003b: det_worker

status: 0XB9, sii902x.retries: 2

sii902x 0-003b: EVENT=plugout

sii902x_poweroff

sii902x 0-003b: exit det_worker

sii902x 0-003b: det_worker

status: 0X1D, sii902x.retries: 2

sii902x 0-003b: EVENT=plugin

sii902x_poweron

sii902x 0-003b: exit det_worker

EXT4-fs error (device mmcblk0p2): ext4_mb_generate_buddy:756: group 19, 9856 clusters in bitmap, 9858 in gd; block bitmap corrupt.

JBD2: Spotted dirty metadata buffer (dev = mmcblk0p2, blocknr = 0). There's a risk of filesystem corruption in case of system crash.

EXT4-fs error (device mmcblk0p2): ext4_mb_generate_buddy:756: group 1, 3 clusters in bitmap, 0 in gd; block bitmap corrupt.

JBD2: Spotted dirty metadata buffer (dev = mmcblk0p2, blocknr = 0). There's a risk of filesystem corruption in case of system crash.

EXT4-fs (mmcblk0p2): 4 orphan inodes deleted

EXT4-fs (mmcblk0p2): recovery complete

EXT4-fs (mmcblk0p2): mounted filesystem with ordered data mode. Opts: (null)

VFS: Mounted root (ext4 filesystem) on device 179:2.

Freeing unused kernel memory: 200K (c06ba000 - c06ec000)

EXT4-fs error (device mmcblk0p2): ext4_mb_generate_buddy:756: group 2, 474 clusters in bitmap, 507 in gd; block bitmap corrupt.

EXT4-fs error (device mmcblk0p2): ext4_mb_generate_buddy:756: group 7, 147 clusters in bitmap, 97 in gd; block bitmap corrupt.

EXT4-fs error (device mmcblk0p2): ext4_mb_generate_buddy:756: group 8, 21679 clusters in bitmap, 21684 in gd; block bitmap corrupt.

JBD2: Spotted dirty metadata buffer (dev = mmcblk0p2, blocknr = 0). There's a risk of filesystem corruption in case of system crash.

random: init_stage2 urandom read with 121 bits of entropy available

random: nonblocking pool is initialized

EXT4-fs error (device mmcblk0p2): ext4_mb_generate_buddy:756: group 0, 17407 clusters in bitmap, 17409 in gd; block bitmap corrupt.

JBD2: Spotted dirty metadata buffer (dev = mmcblk0p2, blocknr = 0). There's a risk of filesystem corruption in case of system crash.

udevd[760]: starting version 175

NET: Registered protocol family 10

IPv6: ADDRCONF(NETDEV_UP): eth0: link is not ready

init_stage2: failsafe main process (1281) killed by TERM signal

init_stage2: atd main process (1341) terminated with status 1

init_stage2: atd main process ended, respawning

xylonfb video mode: 1280x720-32@60

sii902x 0-003b: sii902x_fb_event event=0x1,

sii902x_fb_event event=[FB_EVENT_MODE_CHANGE]

sii902x 0-003b: Sii902x: setup..

sii902x 0-003b: sii902x_fb_event event=0x10,

sii902x 0-003b: sii902x_fb_event event=0x9,

sii902x 0-003b: FB_BLANK_BLANK

sii902x_poweroff

sii902x 0-003b: sii902x_fb_event event=0x10,

sii902x 0-003b: sii902x_fb_event event=0x9,

sii902x 0-003b: FB_BLANK_UNBLANK

sii902x_poweron

FAT-fs (mmcblk0p1): Volume was not properly unmounted. Some data may be corrupt. Please run fsck.