ADC基板を改版して、またElecrowに製作を依頼しました。 今回は、基板を分離して、(1) FM BPF基板、(2) ADC基板 という二枚構成にしました。 ADC基板がZ-turn boardに接続され、FM BPF基板には+5Vを供給します。

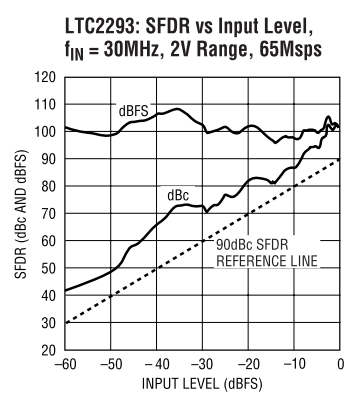

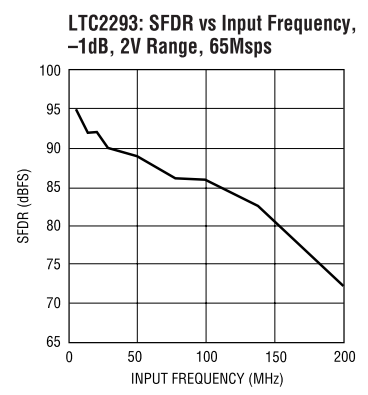

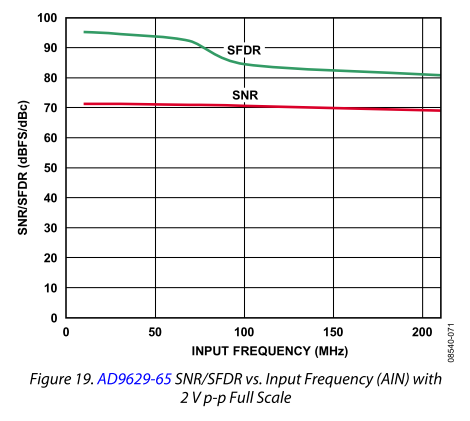

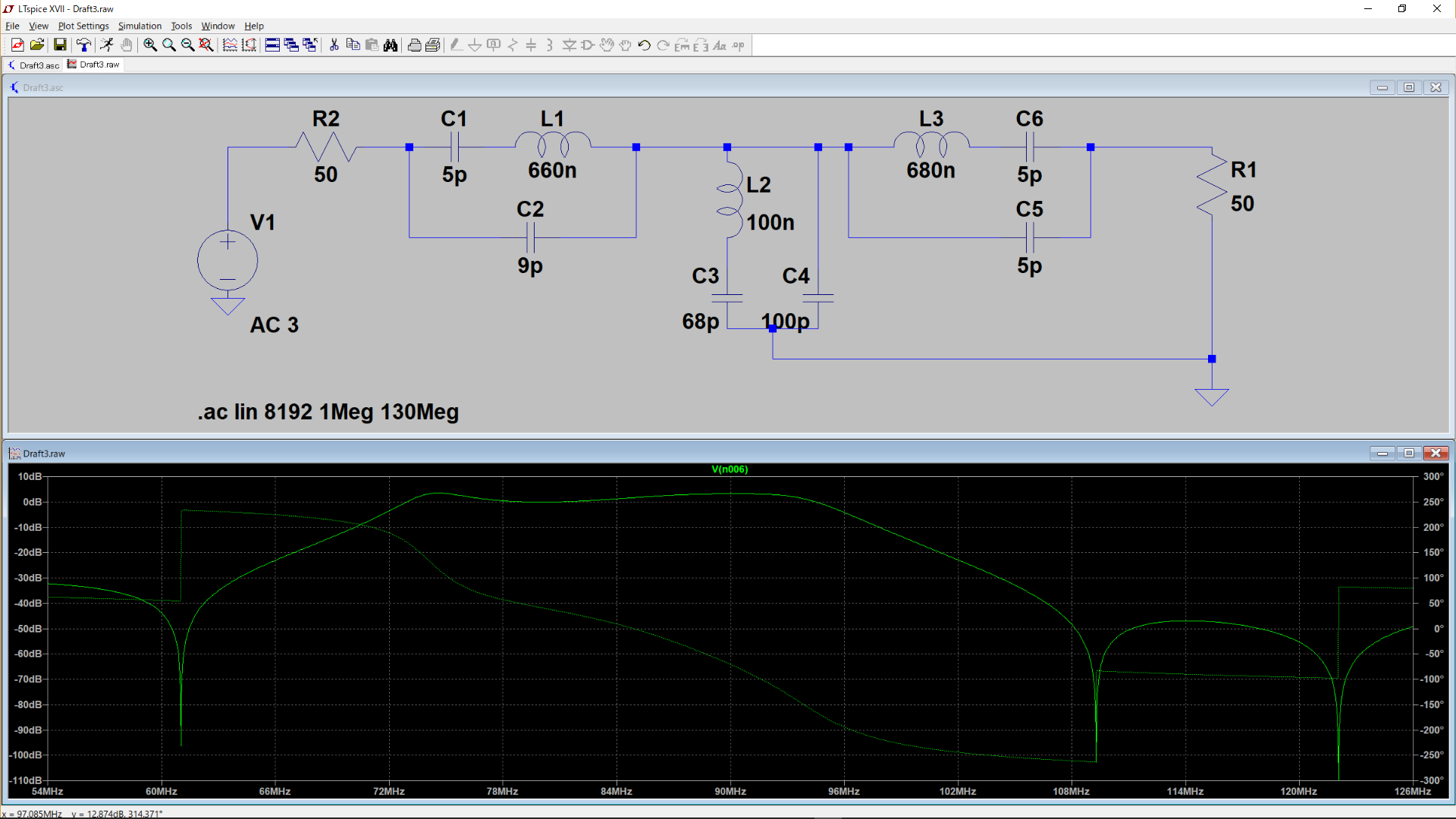

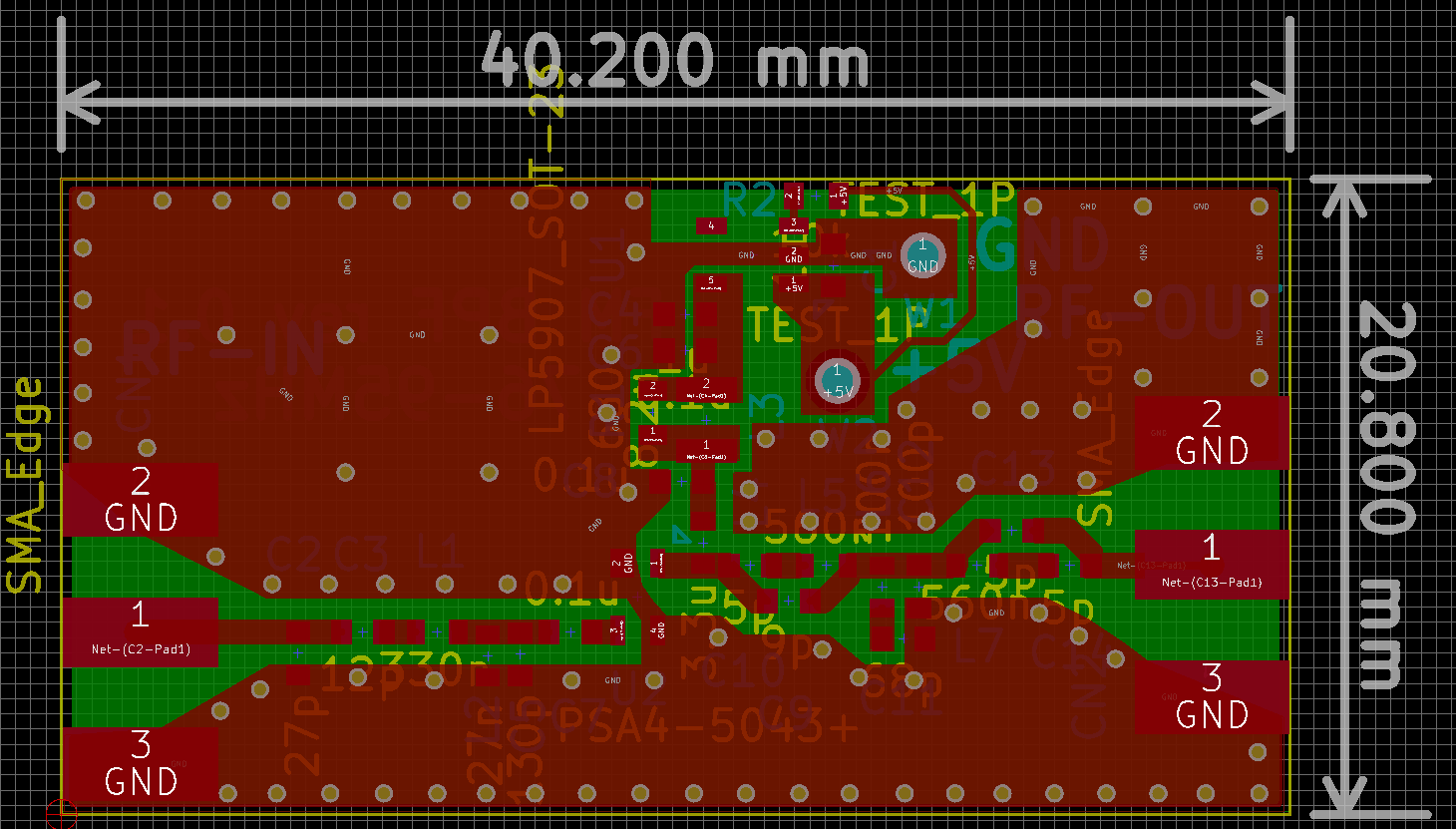

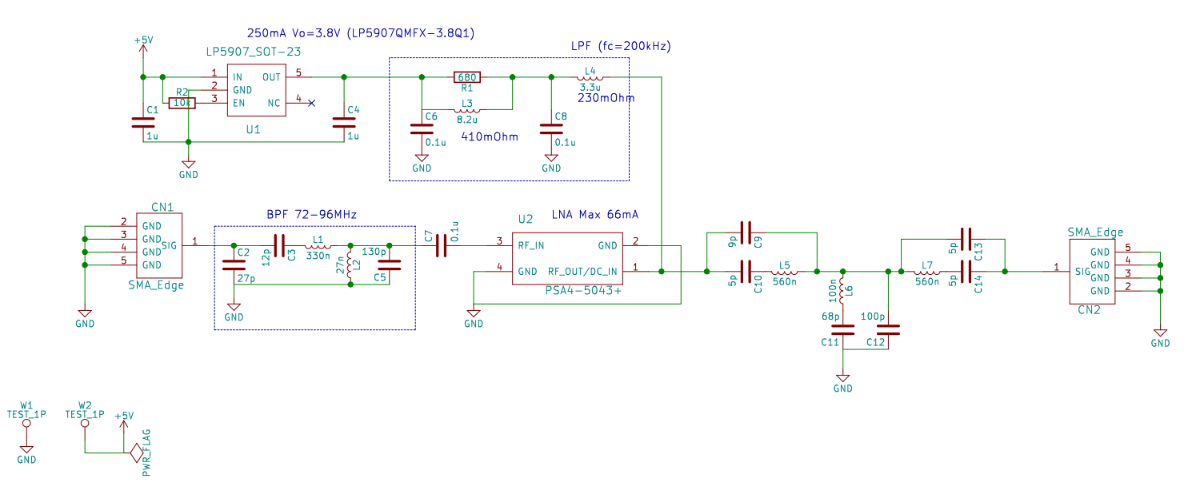

BPF基板は、トラ技2015/4を参考に、76-95MHzを通過帯域とすることを目指しています。

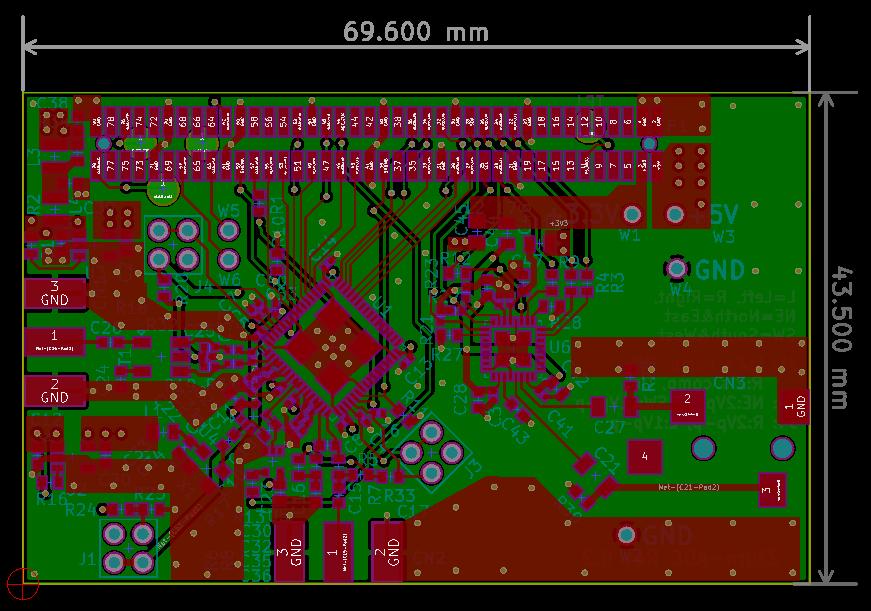

ADC基板は、前回とは以下の部品を大きく変えました。

- 発振器:前回はSiTimeのMEMS発信器+-5ppm品を使用しましたが、これは結構高かった(7USD程度)のに加え、 推奨3.3V駆動であり、今回は3.0Vにしたかったので、+-1ppmのTCXO(3.26USD)を使用しました。 このTCXOはクリップ正弦波出力なので、インバータ(On semiconductor: NC7SVU04)と1MΩ抵抗フィードバックで発振させるようにしました。 このタイプの発振器は使ったことがないので、一応推奨の使用方法通りの回路としましたが、しっかり動作するか少し心配です。

- 差動変換:前回はM/A ComのCenter-tapped transformer (MABAES0060)を使用しましたが、今回はLTC2292の推奨回路に従い、 ETC1-1-13という型番のbalunにしました。

- SMAコネクタ:前回は基板を貫通する、ライトアングルのコネクタを使用しましたが、 各社の評価基板を見てみると、単純に基板エッジのSMAコネクタは、なんだかカッコ良いです。 真似して、今回はエッジタイプのSMAコネクタにしてみました。

その他としては、今回も音声出力用DAC(NAU8822LYG)を載せましたが、いろいろ調べてみたら、 FPGAで比較的簡単に、 同軸デジタル、あるいはS/PDIFと呼ばれるデジタル音声出力ができそうでした。 もっとも、DACとコネクタ含めても部品代は3USDちょっと程度なので、これを削除してデジタル出力のみにしても、 それほどコストダウンはできません。ただ、DAC部はそれほど注意深く設計していないので、 デジタル出力して、外部のDACで変換して音を聞く、というのは実験する意義があるかと思います。 同軸デジタルであれば、RCAコネクタ、S/PDIFであればTOSLINKコネクタを使用します。

TOSLINKコネクタは1,000円以上するかと思っていましたが、 調べていたら100円くらいとお安い(秋月)ものが存在(aitendo)するようですね。digikeyにもありました。 コネクタが高いなら、RCAで良いかと思っていましたが、光だと絶縁できるというメリットがありますからね。

S/PDIFについてはこちらのページも詳しいですね。

それぞれ2枚ずつ製作を依頼しました。これでトータル264USDでしたが、前回のクーポンが使えて、 256.62USDの支払いでした。既に日本円に換算されて、1USD=111.23JPYあたりとなり、 28544JPYでした(送料込み)。

インダクタはこちらが指定した部品を使用してもらえることになりましたが、キャパシタについては Elecrow側が選んだものを使ってもらうことにしました(お値段が高くなりすぎると言われたので…)。 ちょっと特性については心配しています。

以下はおまけのレイアウトです。

ADC基板 (4層 1.6mm)

FM BPF基板 (2層 0.6mm)

FM BPF基板の回路図は次のような感じです。

まだ到着まで2週間くらいかかりそうです。

2017/9/12追記: 基板到着しました。2セット製作したので、 1セットは予備で保管しています。試してみたいという方は、twitterでお知らせください。 ご要望が多ければ、再度製作するかもしれません。