ついに、Elecrowに発注していたADC基板が到着しました。

3 / 9 (木)にPayPalにて支払いを行い、3 / 29に発送のお知らせメールが到着し、3 / 30 (木)に到着しました。

Elecrowから送られてきたL/Tは2-3weeksでしたが、ぴったり3週間で到着です。

3 / 29までは全く音沙汰がなかったので、ちゃんと進んでいるのか、それとも実装に失敗しているなどの問題が起きていないか、心配でした。

完成した写真を送ってくれたという方もいるようですが、私の場合はいきなり発送されました。

OCSの履歴を見てみると、3/28の夜に中国から送られて3/29の午前には日本に到着していました。

配達はさすがに速いですね。

ちなみに、基板2枚実装で241USD, π割引3.14USDで237.86USDでした。日本円で27,784円でした。1USD=116.8円なので、

あまりレートは良くないタイミングでした。

基板の包装は次のような感じでした。

テンション上がります。

ちなみに、かの有名なElecrowガチャは2枚でした(実装したのも2枚)。

ステンシルは入っていませんでした。再度製造を依頼する場合に必要になるので、こちらから頼まなければ保管しておいてくれているのかもしれません(未確認)。

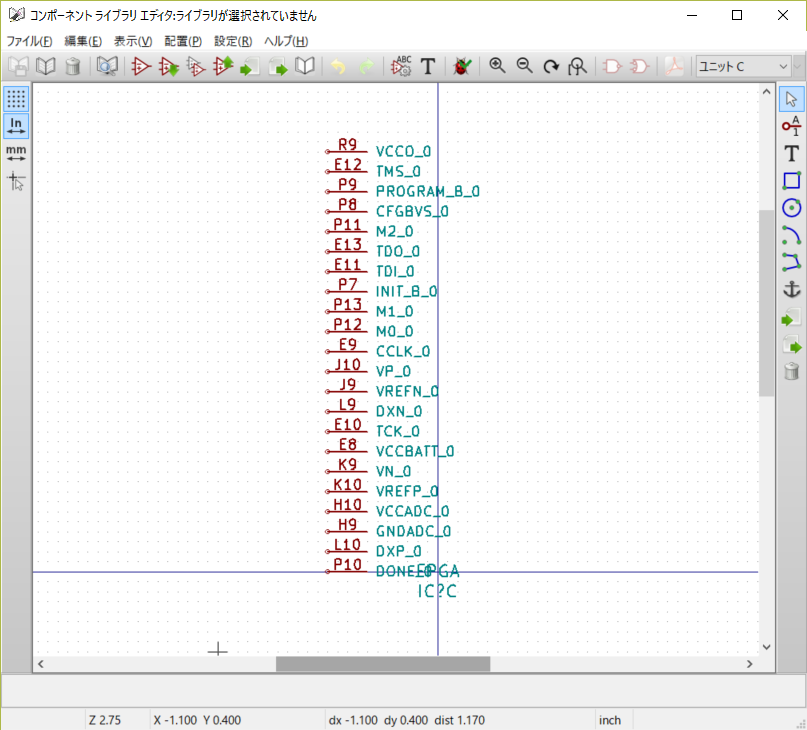

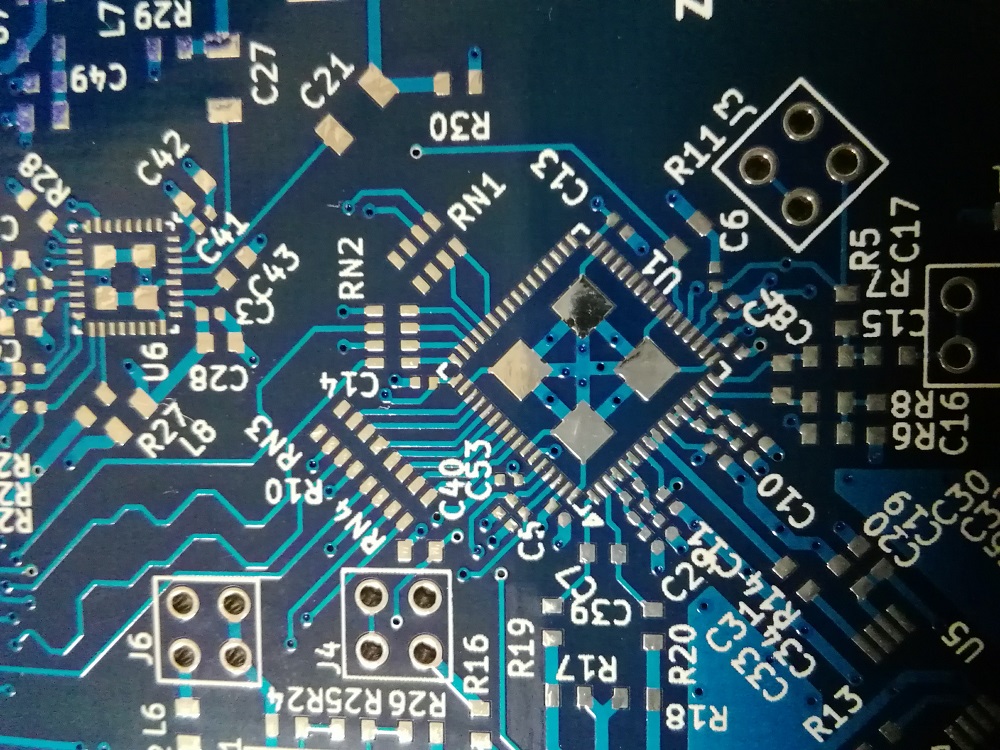

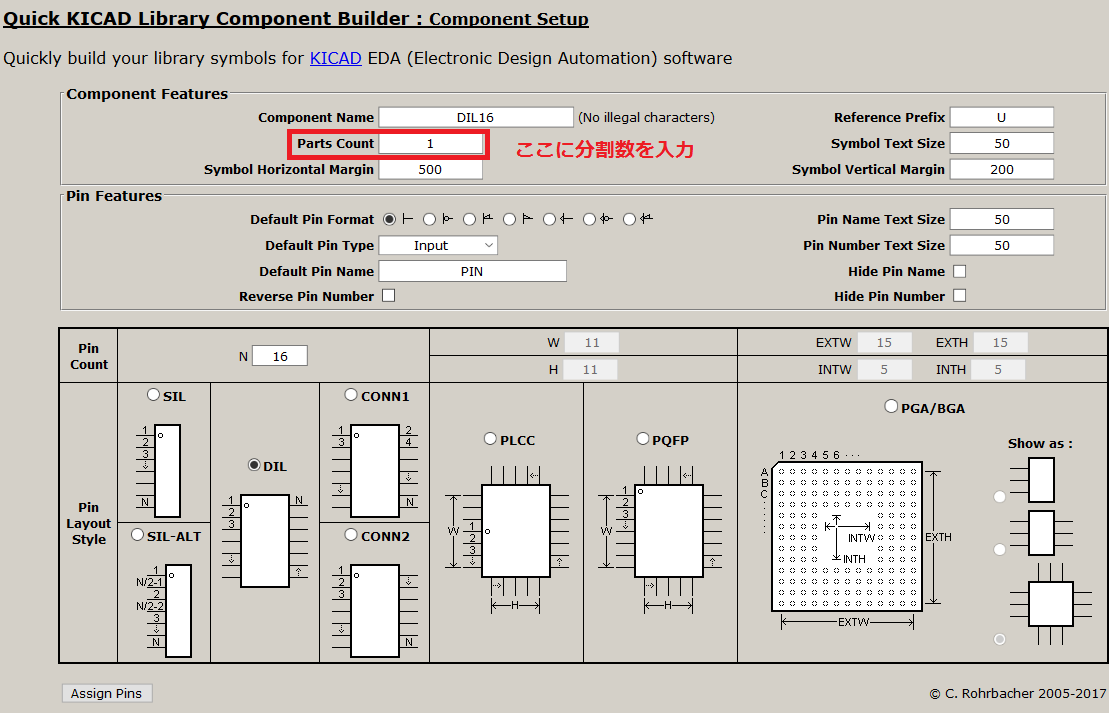

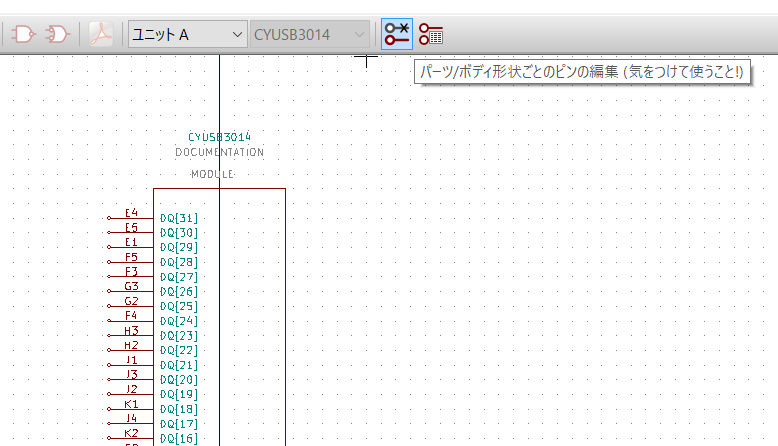

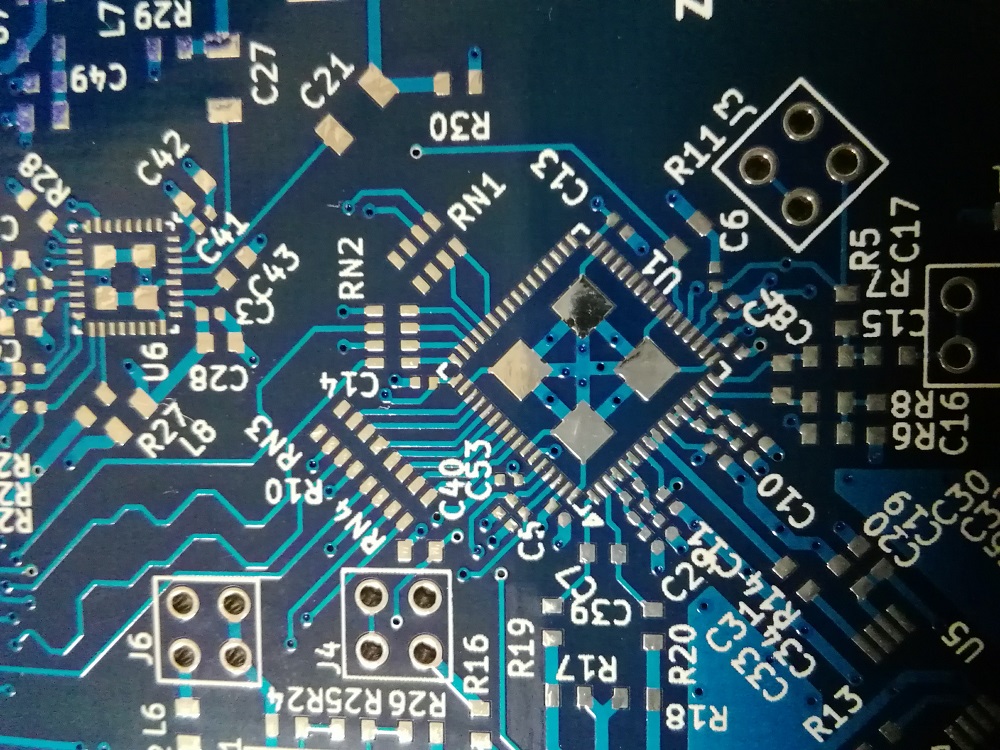

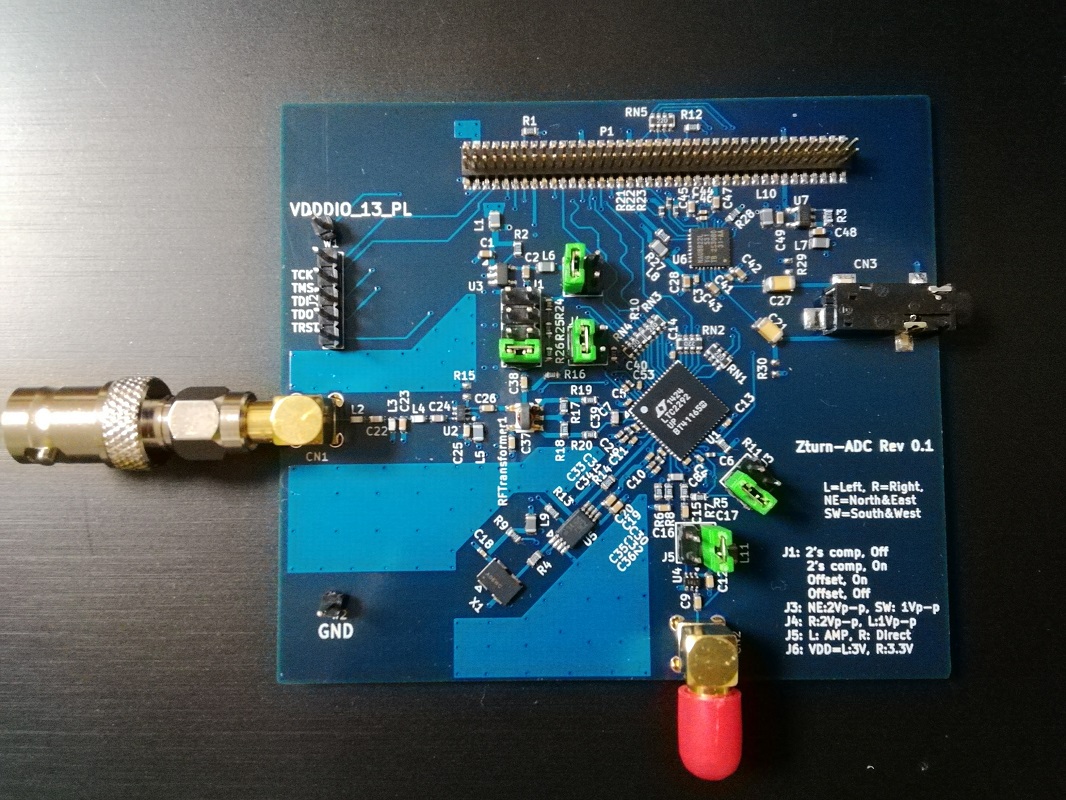

ADCの部分は次のような感じです。

KiCadに習熟していないせいで、若干センターのGNDが甘い気もしましたが、勢いで作ってしまいました。

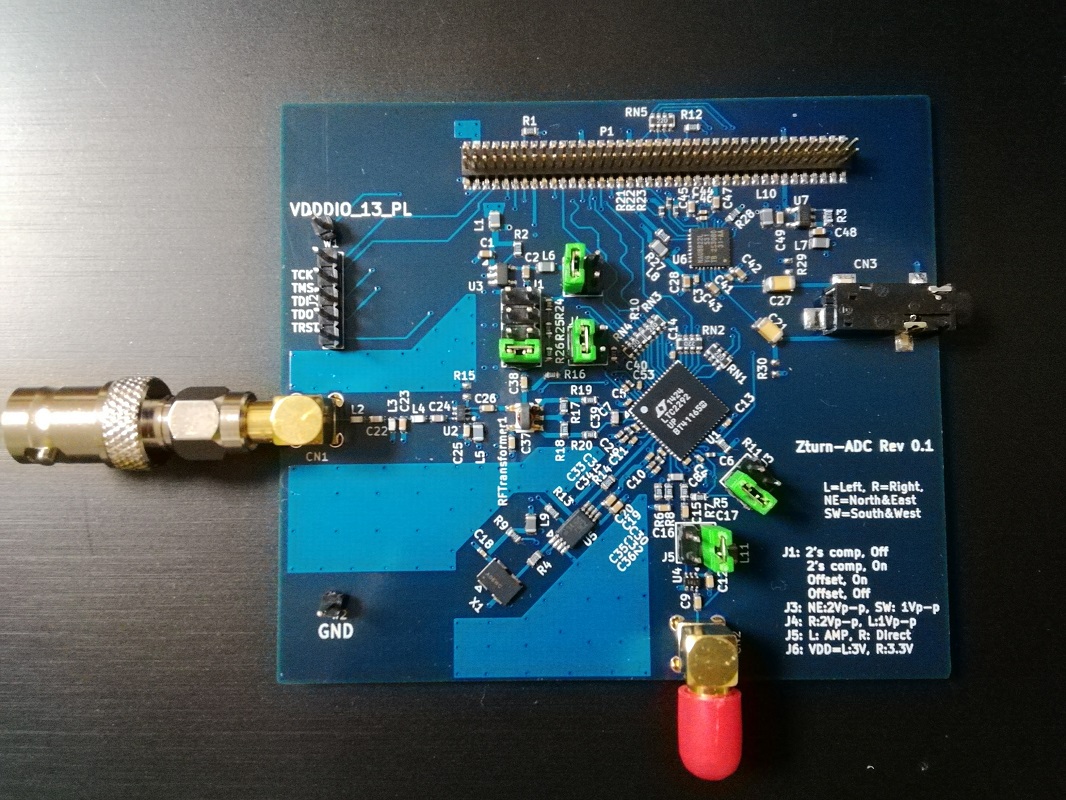

あらかじめ購入しておいたSMA-BNC変換コネクタとジャンパを装着した状態が次です。

うーん、美しい。初めての基板製作で我ながらよくここまで頑張った。

フットプリントがおかしくて墓石になることもなかったようです。

また、ちゃんとDIP部品もしっかり基板に入っています。ヘッドフォン端子はフットプリントが結構変態的だったので、ちゃんと基板に入るか心配でした。

ちなみに、画面下の赤いのは、SMAコネクタを保護しているプラスチックのキャップです。

ちょっと部品間隔が狭すぎるかと予想していましたが、しっかり実装できているようです。抵抗アレイはほとんど横並びです。

自分の実力だと、これほど近接していたらチップ部品の交換はしんどいですね。

右下のジャンパの接続のためのシルクも小さいけどしっかりと見えます。

それにしても、実際の基板ができた時の満足感はすごいですね。もうデバッグはいらない気分になってしまいます。

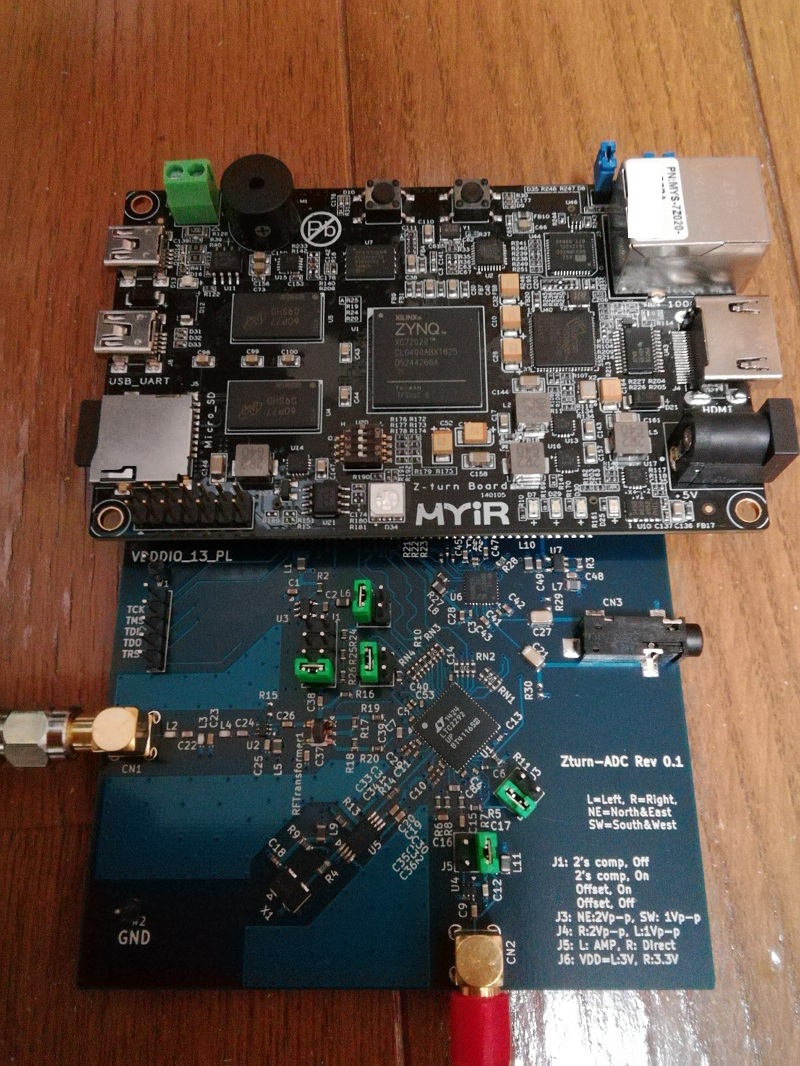

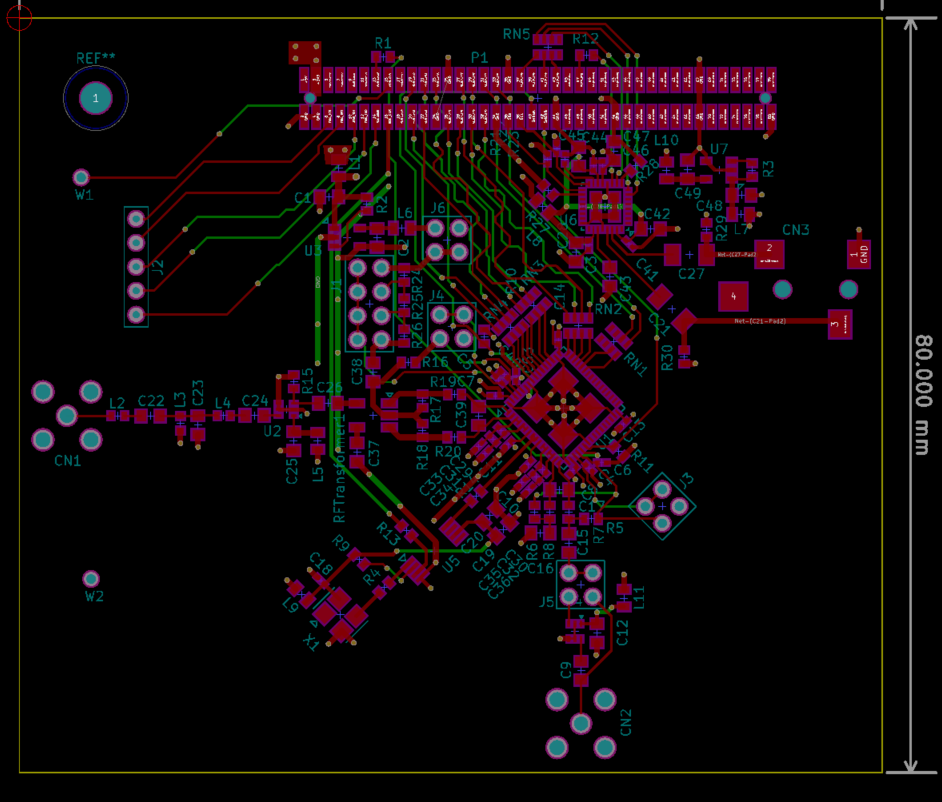

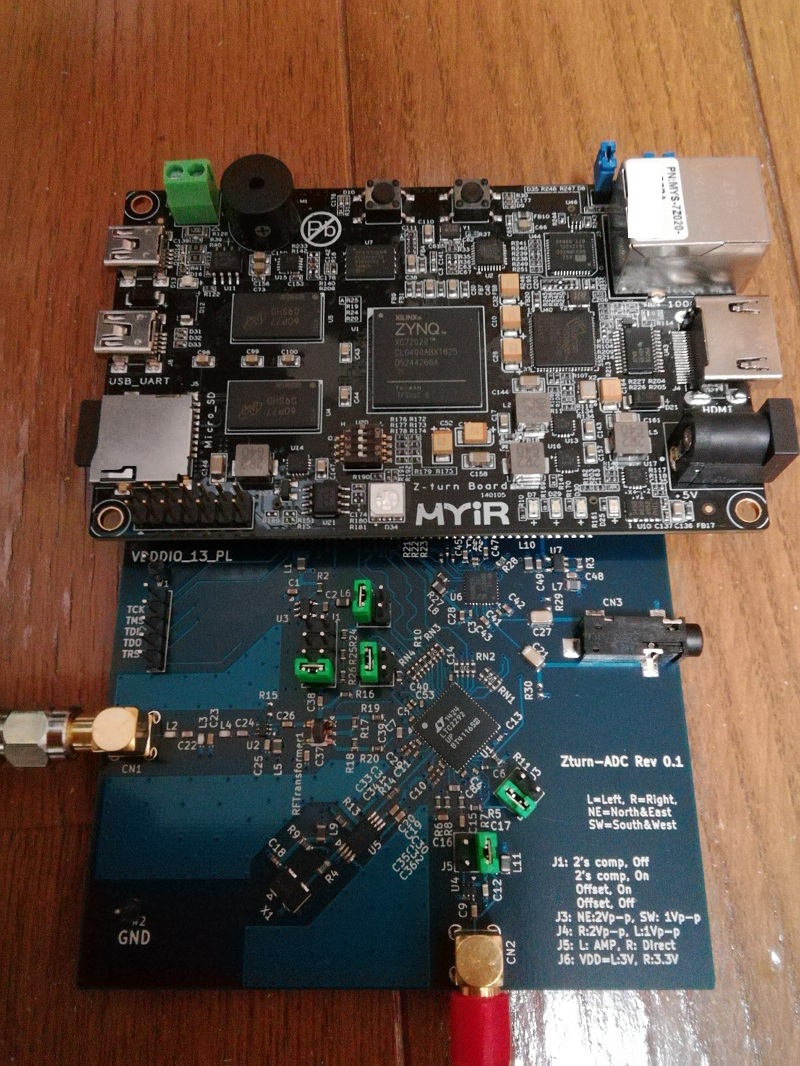

この基板をこれまた購入済みのZ-turn Boardに装着すると、次のような感じです。

さすがに80ピンもあると抜き差しは慎重にやらないと危険です。

1枚の基板はこの80ピンコネクタが少し曲がっているという不具合がありましたが、ひとまず手でなんとか挿入できるくらいまでは真っ直ぐに直しました(汗)。

あ、もちろん、電源を入れる前に電源とGNDがショートしていないことは確認しましたよ。

いよいよ(すぐにアダプタを抜ける態勢で)緊張の電源ON!!

「ピー」 ….. え??? ひとまず電源を抜きます。

おかしい?? ショートしている?? というわけで基板チェック開始。いろいろ調べてみたけど、やはりショートは問題ない。

どうやらJ6のジャンパを入れてADCの電源が入ると音が鳴る。J6がoffだと音はしない。

いろいろ調べてみたところ、どうやらビープを駆動するNPNトランジスタのゲートに接続されているネットがオープン状態なのですが、

そこの電位が数百ミリボルトあがっているようでした。それでトランジスタがONしてしまっているのではないかと思いました

(参考)。

こうなってしまっている原因は不明ですが、ショートは恐らくないことを考えると、

ADC出力が開始されることで、当該ネットに近い他のネットからのクロストークを受けてしまっているのかもしれません。

というわけで、本来ならばビープのネットをプルダウンするのが良い解決策だと思いますが、FPGAで当該ネットをLow駆動することで音は出なくなりました。

ひとまず変更したデザインをQSPI ROMに書き込んで、起動時にコンフィグが終了すれば音が止むようになりました。

ちょっと先が思いやられますが、デバッグを続けます。