ADC基板でのAM/FMキャプチャと復調

ADC基板でAM信号をキャプチャして、 パソコン上のソフトウェアでAM復調を行う、というところまで最低限動作しました。

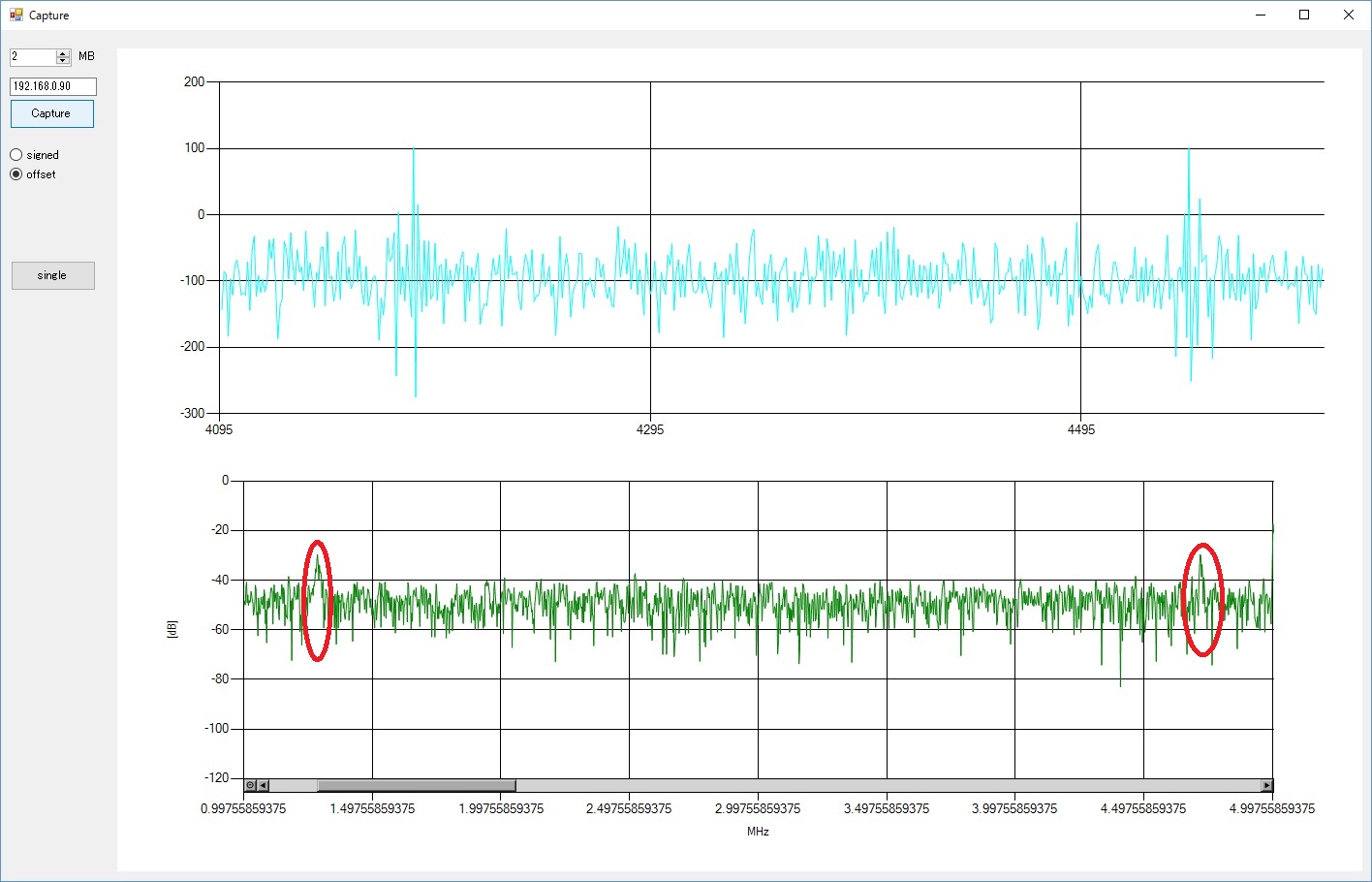

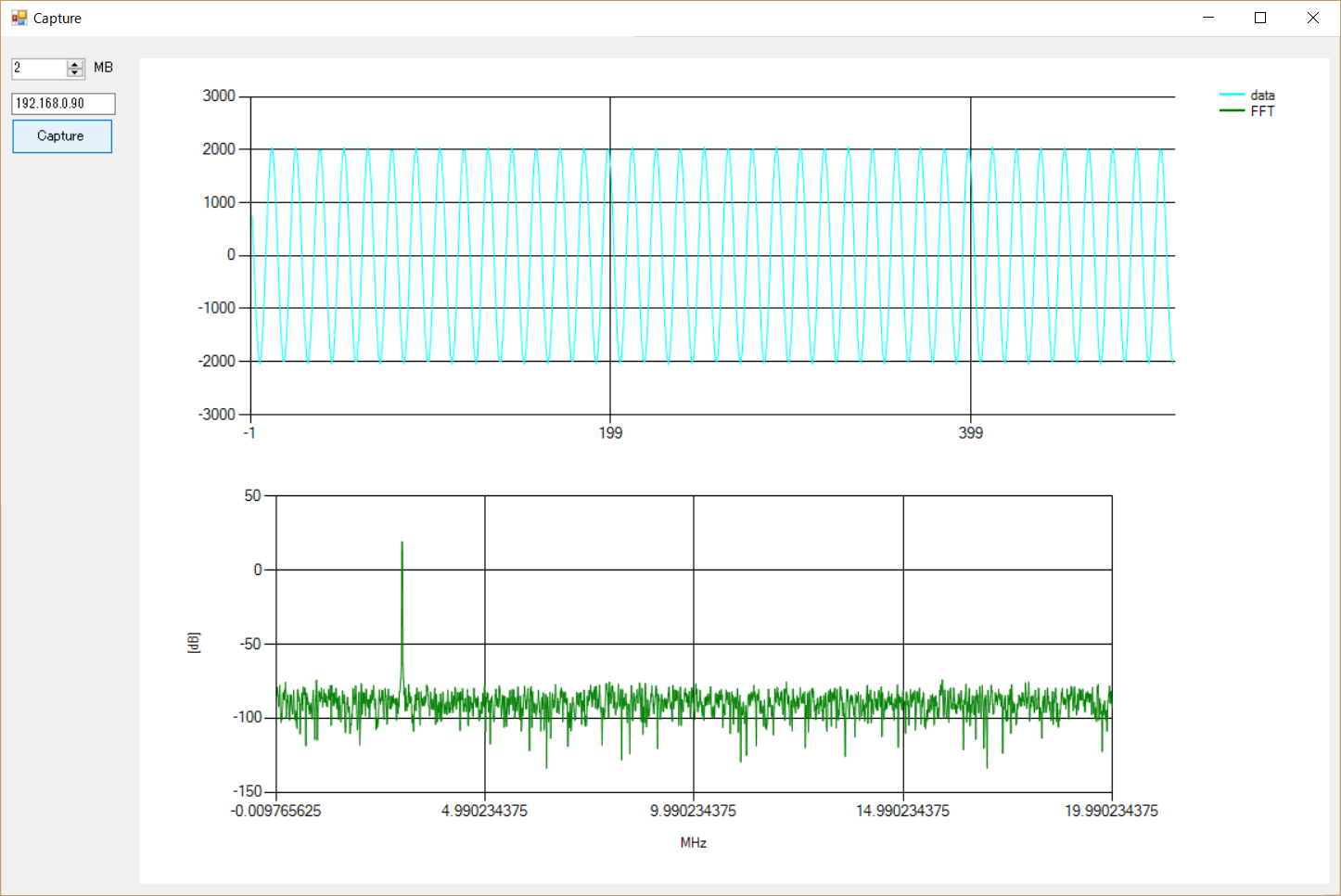

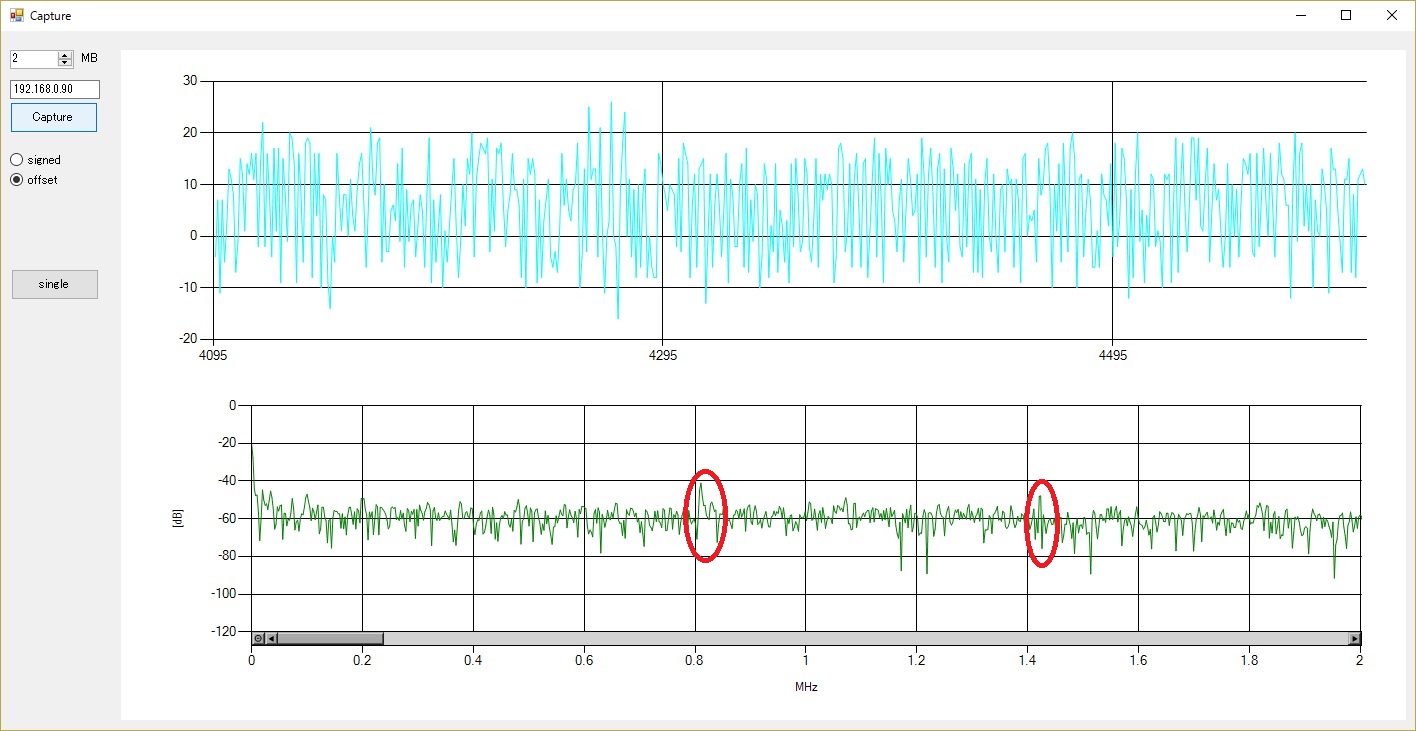

波形を取得しFFTしたときの画面を示します。

赤丸で囲ってあるところは、それぞれ810kHz(AFN), 1422kHz(RFラジオ日本)と思われます。 実際にC#で適当にこしらえたソフトウェアで810kHzをAM復調してみたら、カントリーミュージックが流れていました。

AM復調の流れは、ざっと次のようになります。

- ADCデータ(40MHz@12bit)に、チューニングしたい周波数のsin,cosを生成(NCO)してそれぞれ掛け算してI, Qデータを得る

- I, Qデータを4ステージCICフィルタで1/32に落とす(1.25MHz)

- 続いてFIRフィルタで2/5倍(500kHz)、2/5倍(200kHz)、6/25倍(48kHz)と変換を行う。2/5倍で使用する係数は51タップ、遮断周波数0.2fs。 6/25倍で使用する係数は51タップ、遮断周波数0.04fs。

- 48kHzまで落としたI, Qデータからsqrt(I^2+Q^2)を求めて振幅を求める(AM復調)。 この値をwav形式(モノラル)でファイルに出力する。

SDRについては勉強中の身なので、上記のタップ数や遮断周波数の設定などはあまりよろしくないのかも? しれません。 現状NCOとFIR演算は整数演算ではなく、浮動小数点演算を用いています。 また、FIRのために実装したポリフェーズフィルタもコードが正しいか、まだちょっと不安です。

ただ、上記画面からもわかるように、他にも954kHz(TBSラジオ, 100kW)や1134kHz(文化放送, 100kW), 693kHz(NHK第二, 500kW)などの、出力が大きい局の信号がほとんどとれていません。

Wikipedia - AFNによれば、AFNは出力が50kWらしいので、 他の局も十分受信できても良いように思います。 手元にちゃんとしたAMアンテナが無いので、FMロッドアンテナを基板に装着しているのですが、それが原因なのか? それとも、サンプリングの折り返しなどの原因があるのか(AM側の入力はBPFなどを一切設けていない)? まだ不明です。

また、810kHzなども、「なんとか聞こえる」という程度であり、お世辞にも音質は良いとは言えません。 所有している乾電池式ポータブルラジオの方がはるかに音質が良いです。 もっとも、これについては復調処理に問題があるのかもしれません。

4/5追記: やはり間違いがありました。Wikipedia - サンプリング周波数変換 の通り、a/b倍の周波数変換をするときには、変換後の周波数の1/2の周波数を遮断周波数としなければいけないようです。 上記の設定だと、変換後の1/2fs以上の周波数が折り返してしまいます。 そういうわけで、2/5倍に使用する係数は0.1fsを遮断周波数とし、6/25倍に使用する係数は0.02fsとしました。 また、タップ数もそれぞれ71, 255に増やしました。 そうしたら音質が(まだまだ十分ではないですが)かなり改善されました。

4/11追記: さらに変更して、現在の信号処理の流れは次のようになりました。

- ADCデータ(40MHz@12bit)に、チューニングしたい周波数のsin,cosを生成(NCO)してそれぞれ掛け算してI, Qデータを得る

- I, Qデータを4ステージCICフィルタで1/32に落とす(1.25MHz)

- 続いてFIRフィルタで2/5倍(500kHz, fc=156.25kHz)、2/5倍(200kHz, fc=62.5kHz)、3/5倍(120kHz, fc=48kHz)、2/5倍(48kHz, fc=15kHz)と変換を行う。 使用する係数は255タップ。2/5倍で使用する係数の遮断周波数は0.0625fs。3/5倍で使用する係数の遮断周波数は0.08fs。 上記の通り、2/5倍で0.1fsとすることもできるとは思いますが、それだと1/2fsで-3dBしか落ちませんので、 周波数変換後の高音部にかなりエイリアスが入り込んでしまうと思います。

- 48kHzまで落としたI, Qデータからsqrt(I^2+Q^2)を求めて振幅を求める(AM復調)。振幅が符号付き16bitに収まるようにゲイン調整を行う。 この値をwav形式(モノラル)でファイルに出力する。

追記終わり

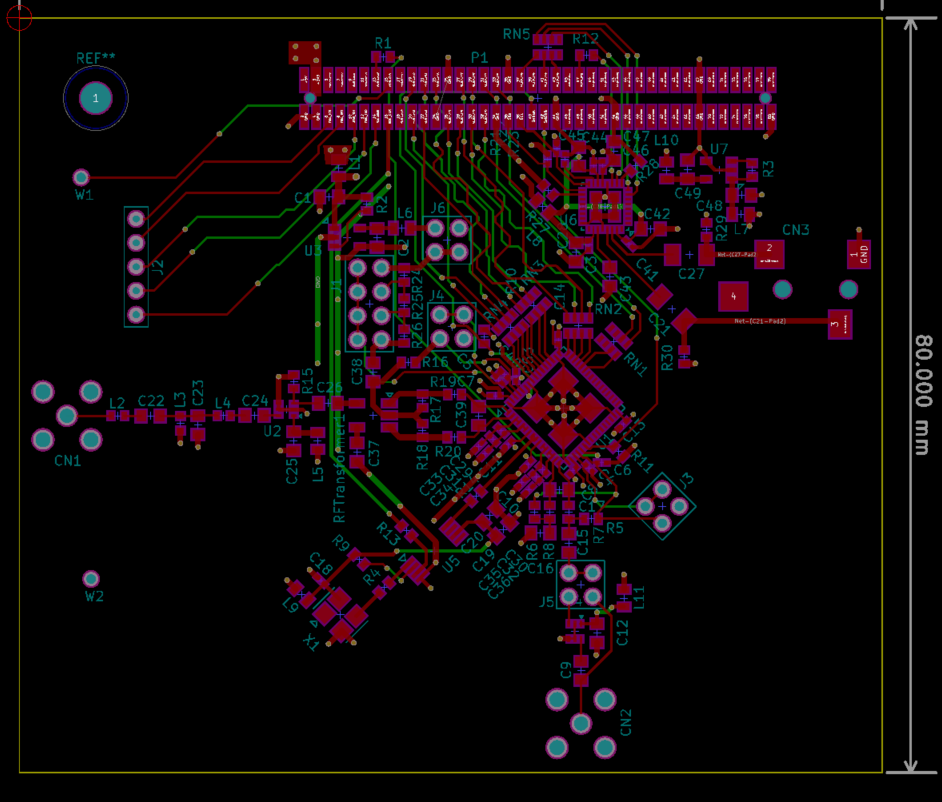

ちなみに、FM側の入力波形を見てみると、次のようになっています。