FMステレオ復調のところは、時間が無くて取り組めていません。

その間に、基板の性能の方を調べて見たくなり、いろいろとオシロスコープを物色しました。

最初はTektronixの中古をヤフオクなどで落とそうかと思ったのですが、最終的には新品を購入してしまいました。

大体100MHzの帯域が測定できる必要があります。それと、FFTも欲しいです。

安くて確実そうなのはRIGOLのDS1054Zかと思いましたが、

最終候補になったのは、HantekのDSO5102Bと、

SiglentのSDS1202X-Eでした。

前者は大体339USD, 後者は379USD程度です。

SDS1202X-Eは、I2C, SPI, UART, CANなどの信号のデコード機能も持っているのが優位点でした。

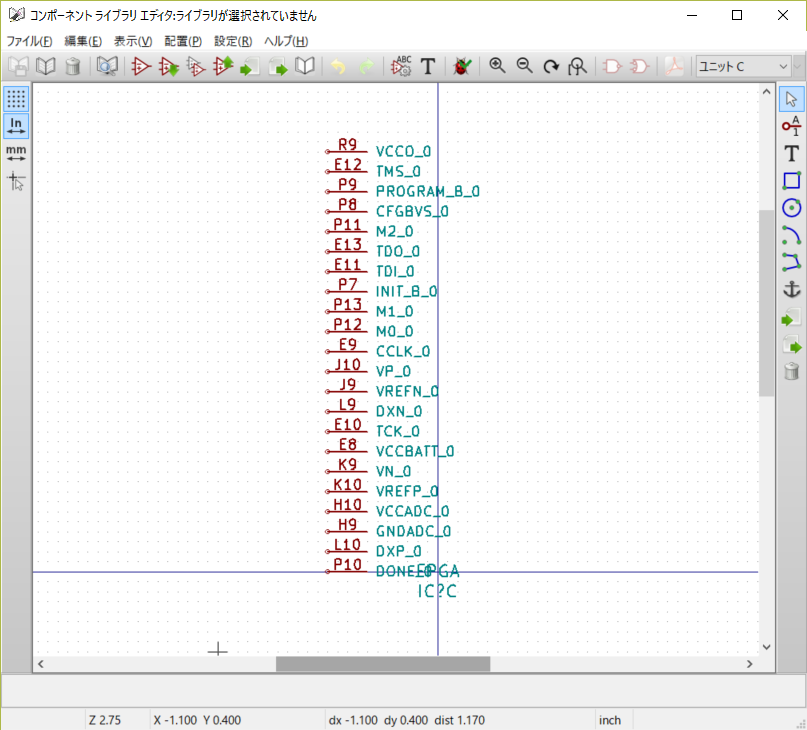

また、SDS1202X-Eの方が新しいです。こちらによると、Zynqの7020を使用しているようです。

結局、SDS1202X-Eを購入しました。最初はAmazon.comから買おうかと思いましたが、

調べてみたらAliExpressにて送料無料で購入できることがわかり、

そちらに出店していたSains Electronix Storeから購入しました。

6/15(木)の夜に注文して、6/19(月)には到着しました。早いです。

(2019/1/12現在、日本のAmazonからも購入できるみたいです)

注文したら、すぐにお店から、“USコードを選択していたけど、EUコードしか在庫がないんだよ。

USコードは2週間待ちなんだけど、EUコードで送っても良いかい? (意訳)“という内容のメッセージが届きました。

“いやいや、待っても良いからUSコードでお願い。でもできるだけ早くね! (意訳)“と返しました。

そうしたら翌日6/16(金)には発送のお知らせが来たので、まさかEUコードが添付されているのではないか、

とはらはらしましたが、到着した商品を確認したら、ちゃんとUSコードが添付されていました。

うっかりしていたのは、このコードは3ピンタイプだったので、家にある電源プラグに接続するために変換プラグを購入する必要がありました。こういうやつですね。

あるいは3ピン2ピンケーブルでも良いですね。

AliExpressは初めて使いましたが、楽天のように店舗によって対応がまちまちのようです。

今回使用した店舗は迅速で満足でした。Web上での評価も高いようです。梱包も問題ありませんでした。

当たり前ですが、プローブが2本ついています。写っていませんが、USBケーブルも添付されていました。

オシロ本体です。とりあず、電源を入れてプローブ補正だけしました。

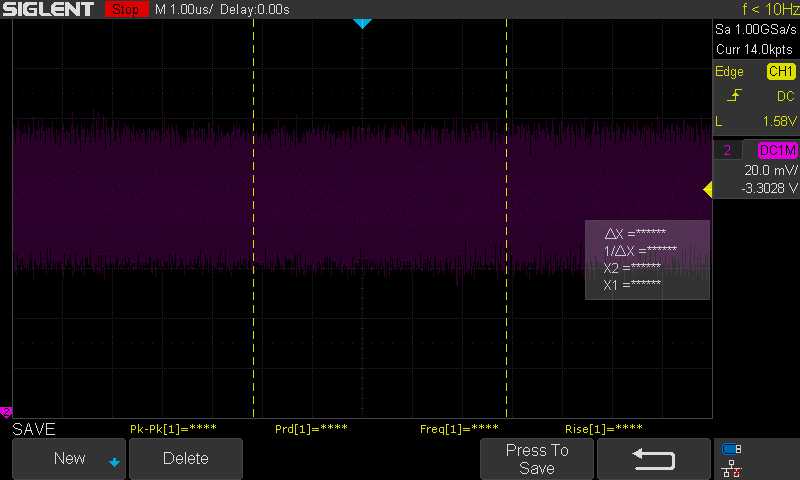

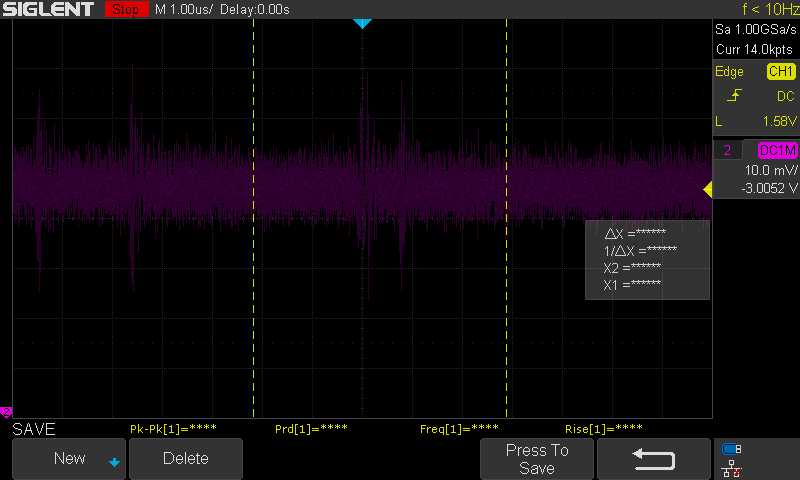

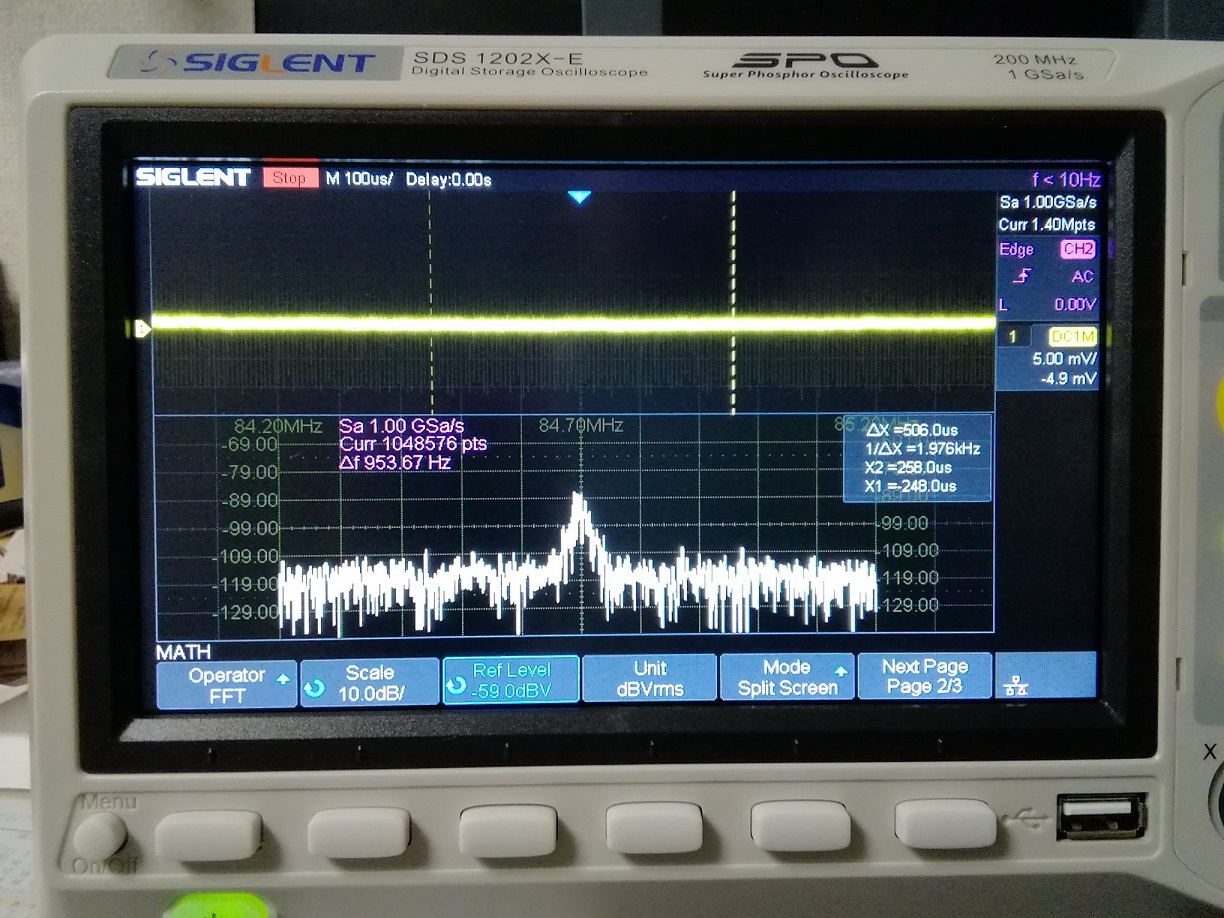

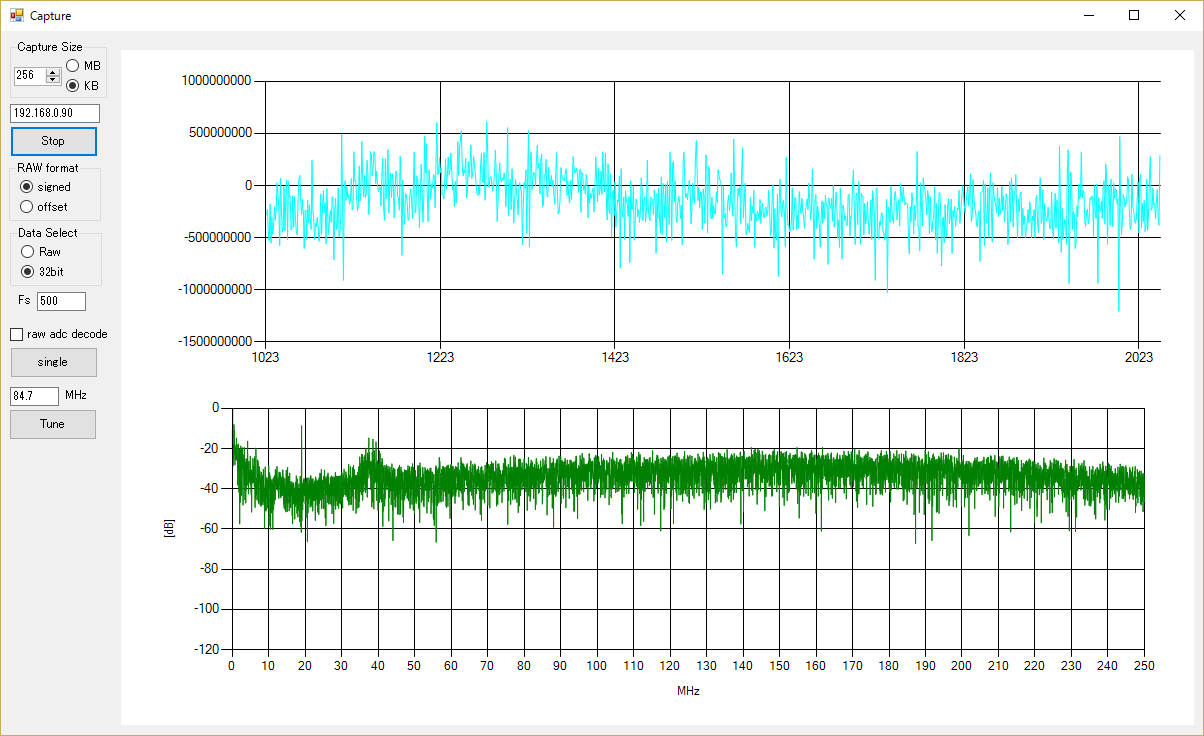

早速ADC基板を少し測定してみました。

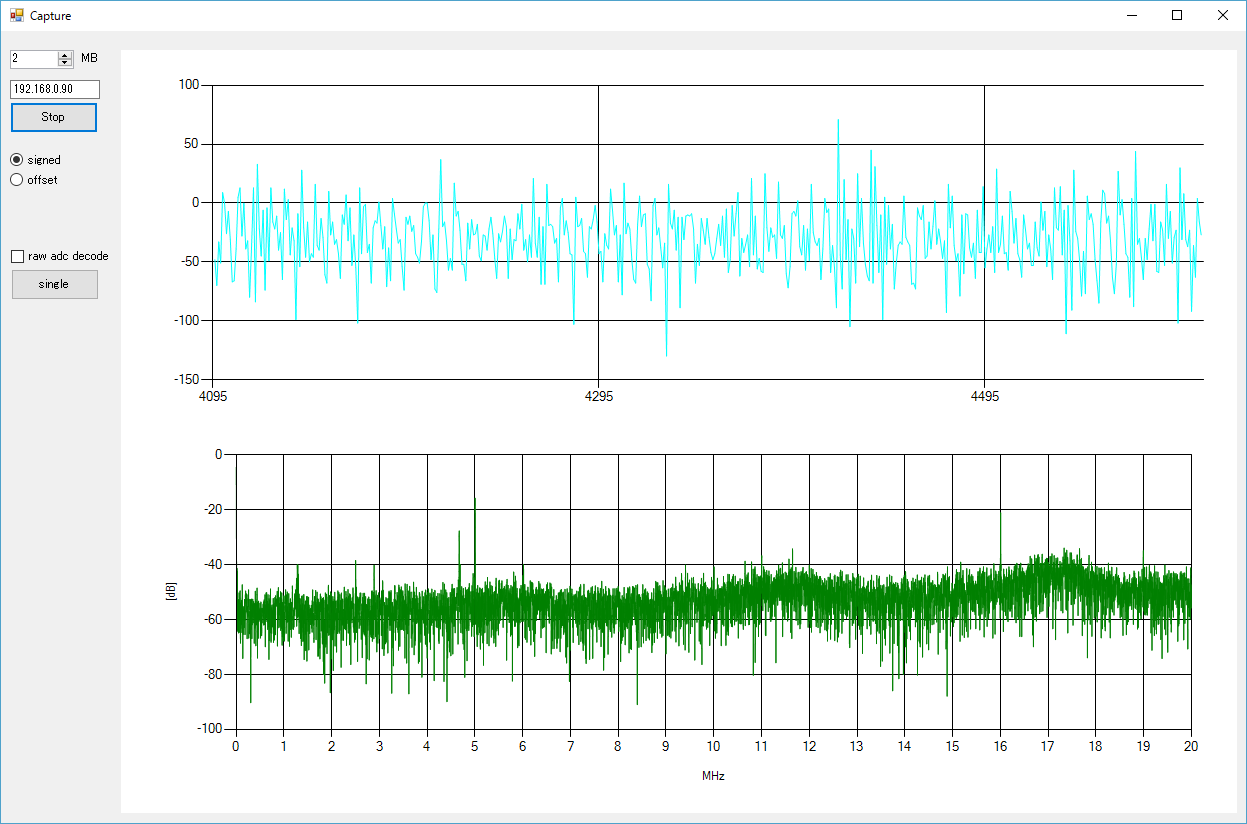

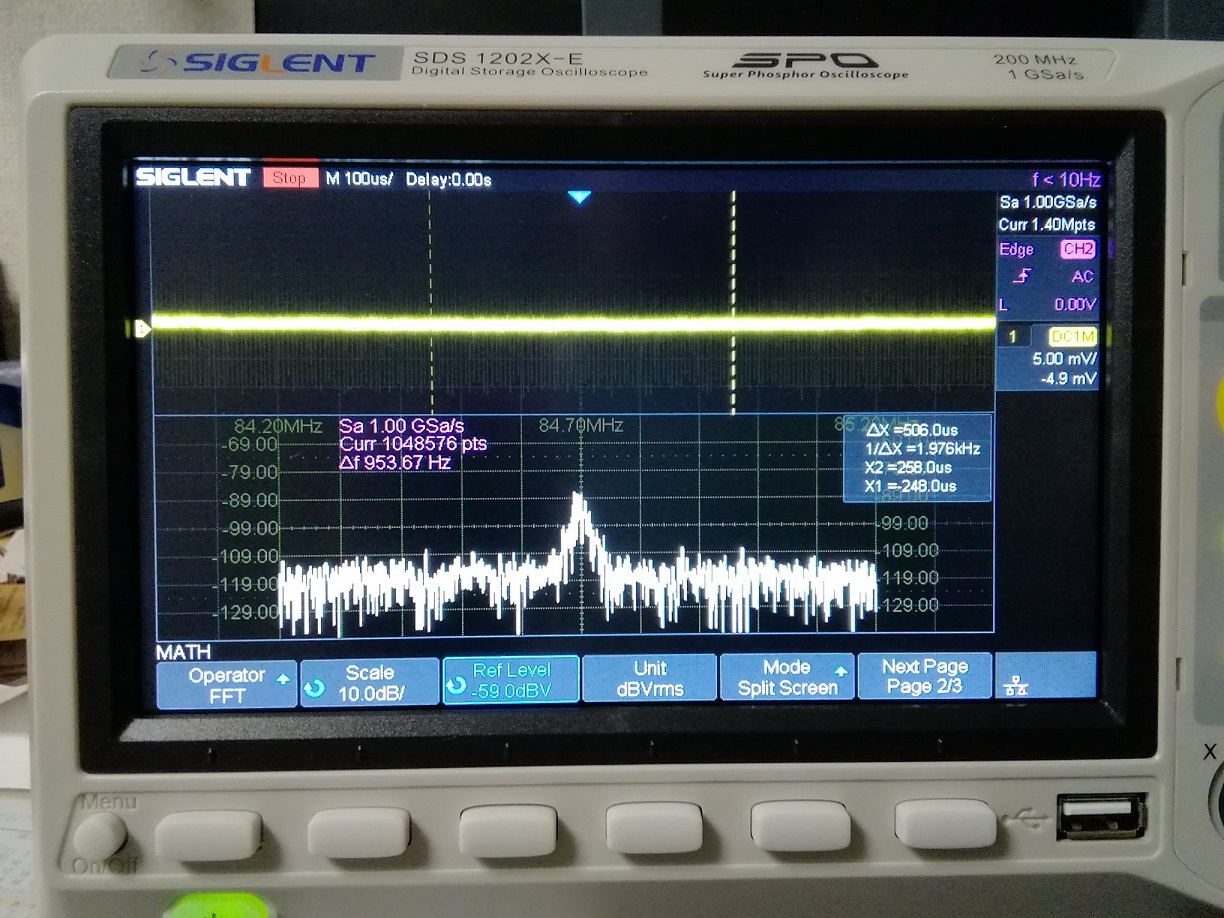

基板に電源は投入せずに、FMアンテナを接続して、BPFの後の個所にプローブを当て、FFTをしてみた結果が次になります。

ちなみに、GNDは基板上に立てたピンでとっているので、あまり良くないかもしれません。

そういえば、画面キャプチャも本体でできるはずですね。わざわざ撮影する必要は無かったですね。

それは置いておいて、上の画面では84.7MHz近辺を拡大しています。Y軸の単位はdBVrmsになっています。

大体20dB位は信号が出ているようですね。

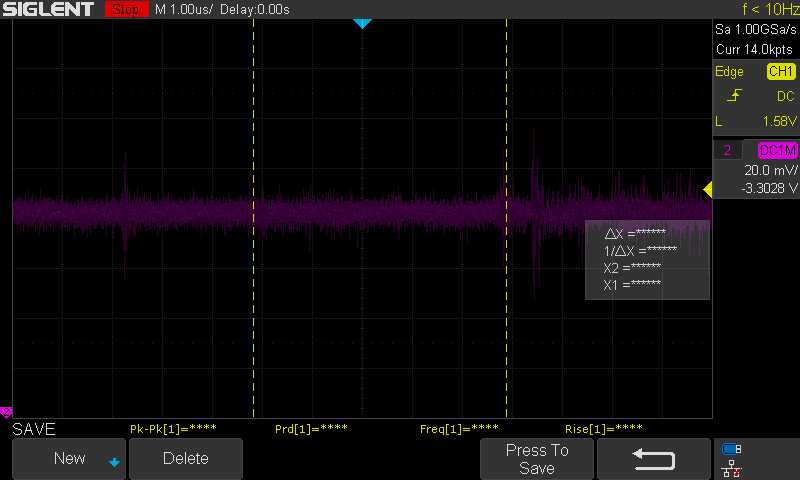

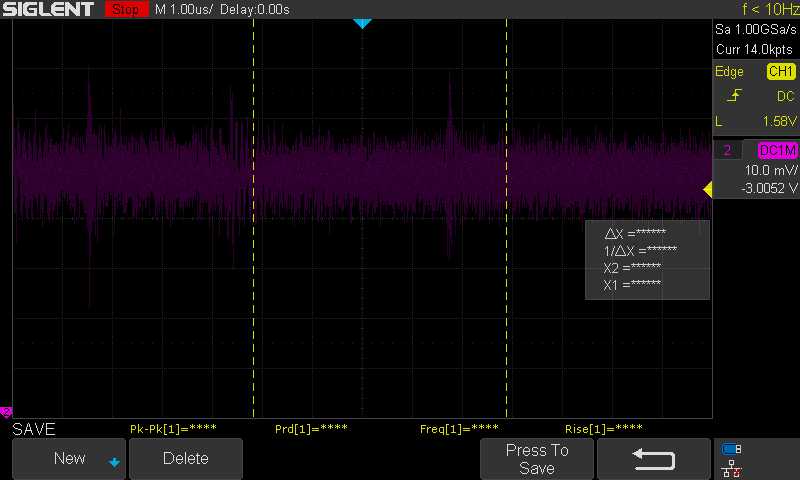

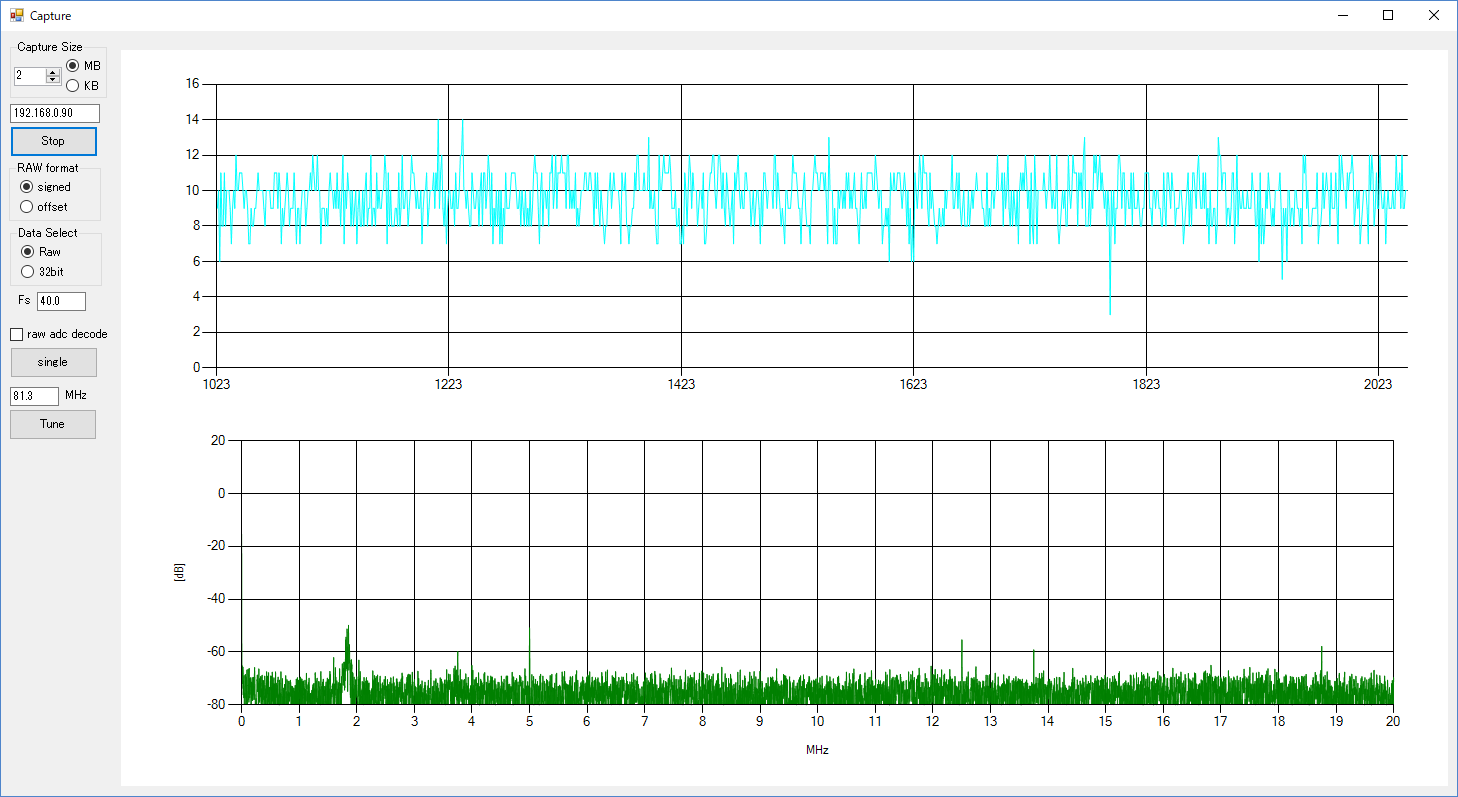

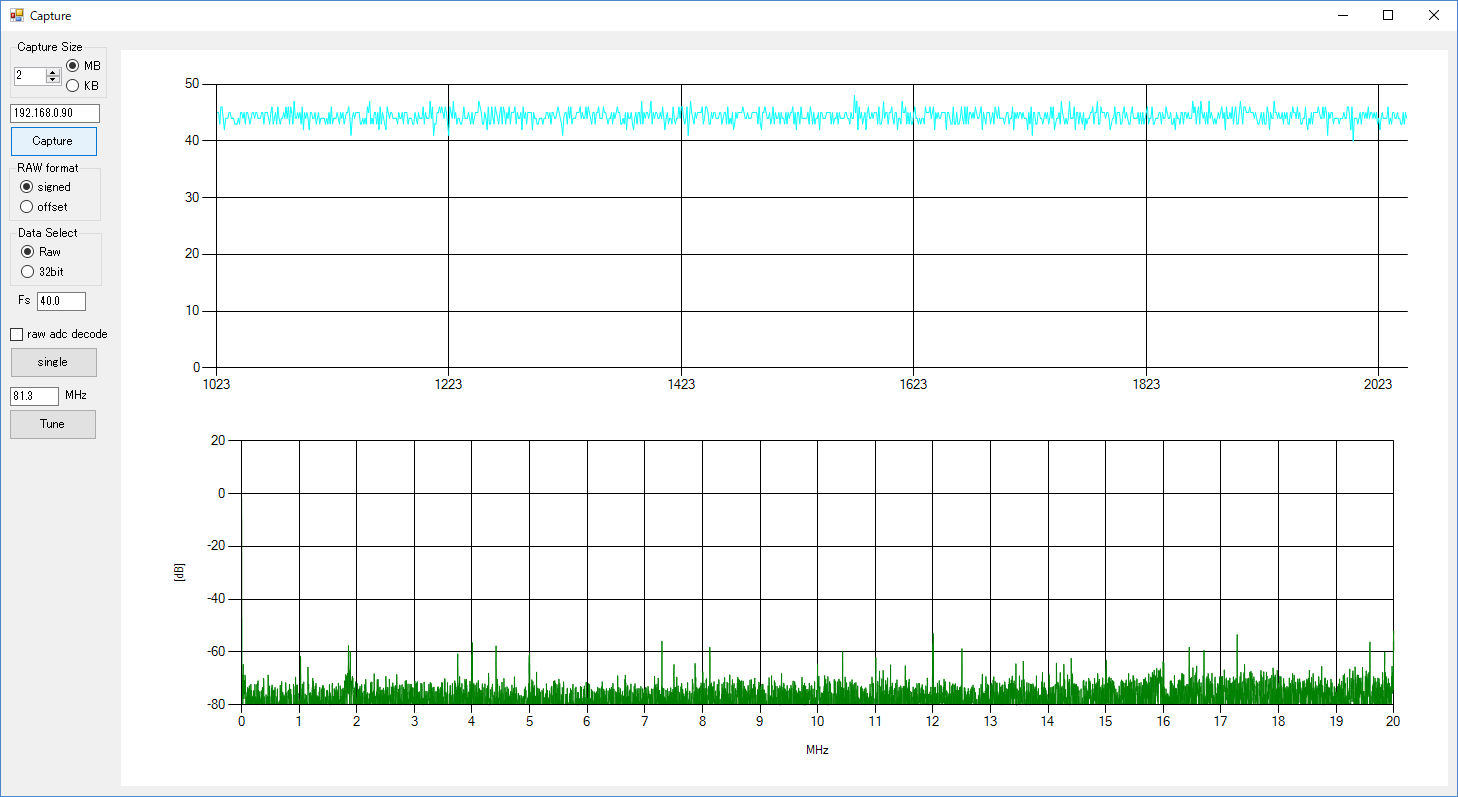

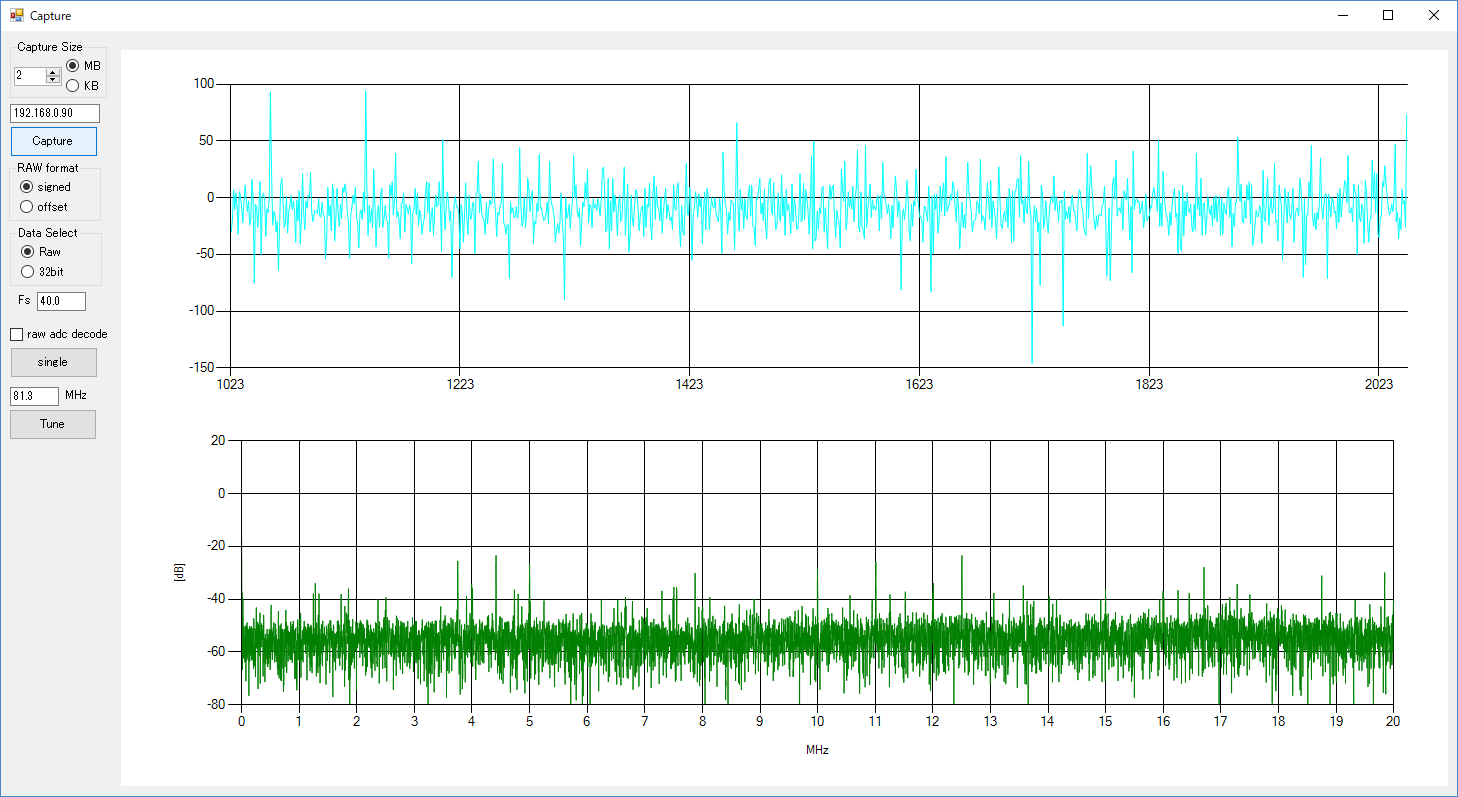

問題は、電源を投入した時の様子です。順次調べていこうと思います。