7シリーズFPGAのBUFMRを有効活用する

Xilinxの7シリーズFPGAを使用していると、Implementation時にCLOCK_DEDICATED_ROUTE=BACKBONEを設定しないと他のクロックリージョンのCMTを駆動できないよ、といったエラーが出ることがあります。

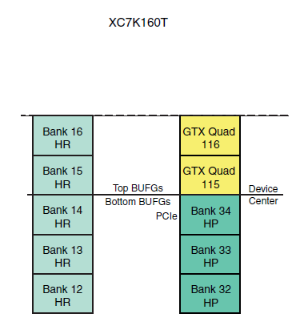

多くの場合、下図(Kintex-7 160T)を例とすると、Bank15とBank14のCMTを同一のクロックで駆動しようとしたときに、このエラーが発生します。

このような場合、もちろんメッセージに従ってCLOCK_DEDICATED_ROUTE=BACKBONEを指定することも可能ですが、 “その場合は最適ではないよ(sub-optimal)“といった怪しい内容を承諾することになります。

でも実は、それ以外にもあまり知られていない(かもしれない)逃げ道があるのです。

それはBUFMRを使用することです。BUFMRは、入力されたバンクの上下も駆動できます。 例えば、上図でBank15(のMRCCピン)に入力されたクロックは、Bank16, Bank14のCMTを駆動することができます。

それで、MRCC pin->BUFMR->BUFR->CMTというように接続すれば、Bank15に入力されたクロックでBank14-16のCMTをエラー無く駆動することができます。

SRCCにクロックが入力されていた場合は… 残念ですが、CLOCK_DEDICATED_ROUTE=BACKBONEを指定してください。