XilinxのFPGAをKiCadのコンポーネントライブラリにするPerlスクリプト

XilinxのFPGAをKiCadで使用するために必要なコンポーネントライブラリ(のたたき台)を作成するためのやっつけPerlスクリプトを作成しました。

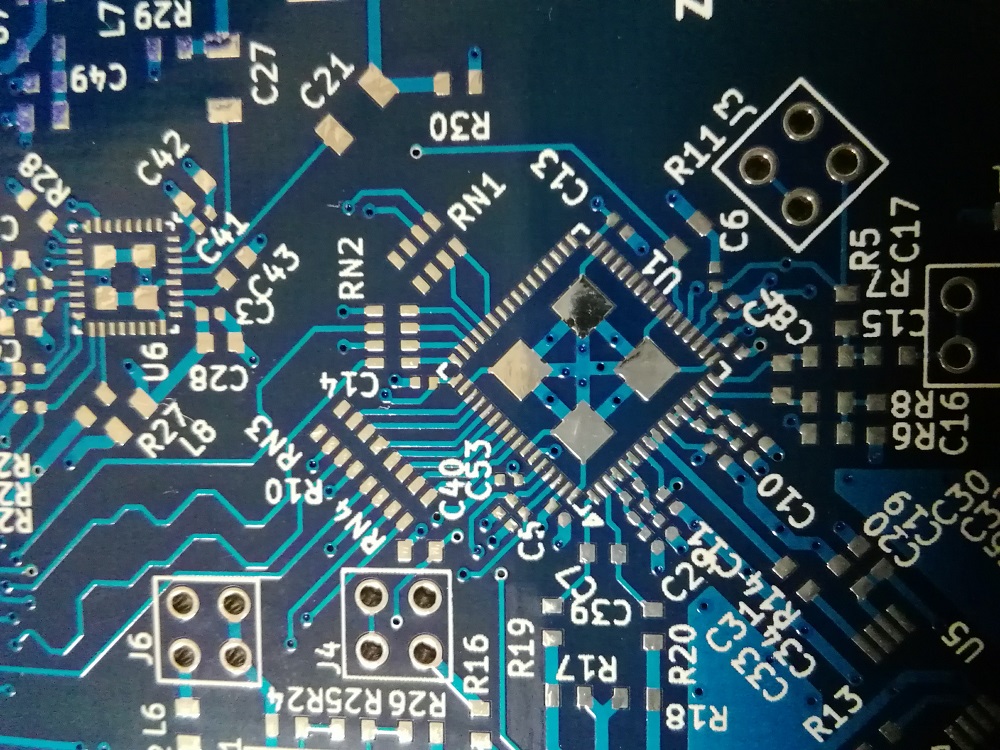

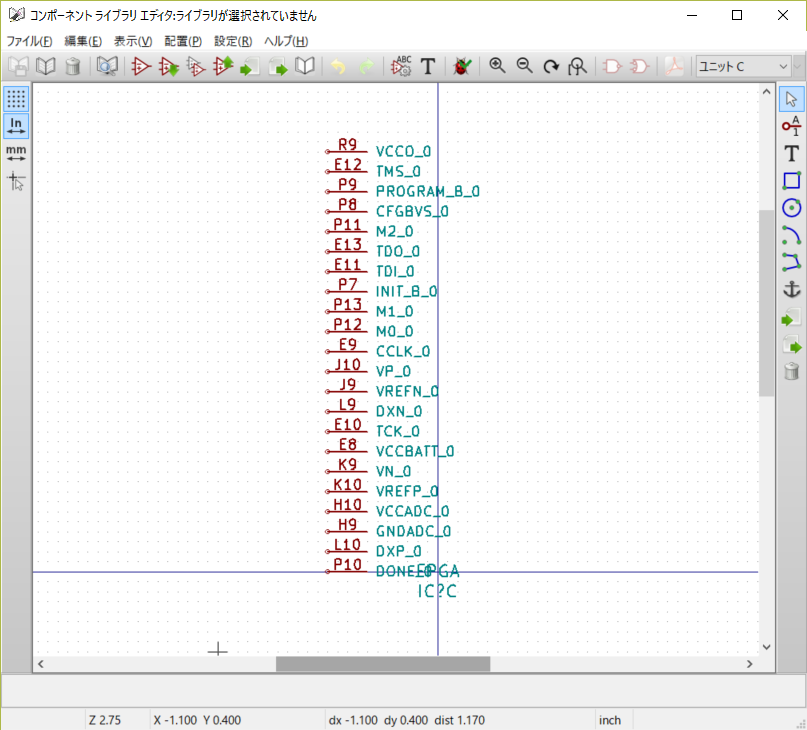

以下にソースを張っておきます。無保証です。使用方法は、Usageにも簡単に書きましたが、 まず、XilinxのページからPackage Device Pinout Filesを持ってきます。 例えば、Artix-7ではこちらのページからデバイス一覧のリンクをたどれます。次に、標準入力からスクリプトに流し込み、標準出力を*.libにリダイレクトします。 このlibファイルをKiCadのコンポーネントエディタで開くと、次のような感じになります。

すいません、矩形の描画はさぼっています。適宜矩形を追加したり、リファレンスを移動したり、 ピンの入れ替えなどを行ってください。 矩形の描画等は複数ユニットのコンポーネントだと、ちょっと注意しないといけません。実際の作業方法については、 KiCadで複数ユニット部品を作るが参考になります。

ピンはバンク毎に別々のユニットに分かれています。 こうするとVCCOも各バンクに属してしまうようです。必要であればlibを直接編集するなりしてください。

#!/bin/perl

# Usage:

# $ wget https://japan.xilinx.com/support/packagefiles/a7packages/xc7a50tfgg484pkg.txt

# $ cat xc7a50tfgg484pkg.txt | perl xilinx_kicad.pl > xc7a50tfgg484.lib

use strict;

my %banks;

# skip header

while (<>){

last if $_ =~ /Pin\s+Pin Name/;

}

while (my $line = <STDIN>){

chomp($line);

last if $line =~ /^\s+$/; # skip footer

my @lst = split(/\s+/, $line);

## foreach my $val (@lst){

## print "$val ";

## }

## print "\n";

push @{$banks{$lst[3]}}, "$lst[0] $lst[1]";

}

my $number_of_banks = keys %banks;

print "EESchema-LIBRARY Version 2.3\n";

print "DEF FPGA IC 0 40 Y Y $number_of_banks F N\n";

print "F0 \"IC\" 0 -100 60 H V C CNN";

print "F1 \"FPGA\" 0 -200 60 H V C CNN";

print <<'END';

F2 "" 0 0 60 H I C CNN

F3 "" 0 0 60 H I C CNN

DRAW

END

my $bank_count = 1;

foreach my $bank (keys %banks){

#my $number_of_pins = @{$banks{$bank}};

#print "Bank: $bank ($number_of_pins pins)\n";

my $i = 0;

foreach my $pin (@{$banks{$bank}}){

#print "$pin\n";

my @val = split(/\s+/, $pin);

#print "\t$val[0]=$val[1]\n";

my $posy = $i * 100;

print "X $val[1] $val[0] -550 $posy 200 R 50 50 $bank_count 1 B\n";

$i++;

}

$bank_count++;

print "\n";

}

print "ENDDRAW\nENDDEF\n";