Ethernetの仕様

イーサネットの仕様についての調査メモ。10Gb/s, 40Gb/sあたりを中心に調査。随時更新します。

規格書はIEEE Std 802.3と呼ばれている。無料でダウンロード可能です。 下記ではPCS/PMAについても仕様を読み解いていますが、 大手FPGAベンダ(Xilinx, Intel)の10G対応トランシーバを内蔵したFPGAでは、 10G Base-RのPCS/PMAについては無料のIPコアを使用できます(参考1, 参考2)。 これらのIPコアとMACの間は、XGMIIが使われます。但し、Ethernetの仕様書のようにDDRではなくSDR動作のため、64bit幅です(156.25MHz)。

802.3uで100Mb/s動作が規定された。802.3zで1000Mb/s動作が規定された。 802.3baで40Gb/s, 100Gb/sが追加された。

802.3-2018の構成は次の通り

Section One: Clause 1から20まで、Annex AからHまでと4A。10Mb/sとMAC、 フレームフォーマットについて。

Section Two: Clause 21から33までとAnnex 22Aから33Eまで。100Mb/sについて。

Section Three: Clause 34から43までとAnnex 36Aから43Cまで。1Gb/sについて。

Section Four: Clause 44から55までとAnnex 44Aから55Bまで。10Gb/sについて。

Section Five: Clause 56から77までとAnnex 57Aから76Aまで。

Section Six: Clause 78から95までとAnnex 83Aから93Cまで。Energy-Efficient Ethernet, LLDP, TLV. Clause 80から95までは40Gb/s, 100Gb/s動作の一般的情報と物理層。 Clause 90は時刻同期プロトコル。

Section Seven: Clause 96から115とAnnex 97Aから115A。

Section Eight: Clause 116から126とAnnex 119Aから120E。200Gb/s, 400Gb/s, 2.5Gb/s, 5Gb/sについて。

ということで、Section Four, Sixあたりを重点的に読む。また、MACについてはClause 2-4で定義されている。

Clause 44.1.4.4.

10GBASE-SRはClause 49 (PCS), 51 (Serial PMA), 52 (850nm Serial PMD)に対応する。

10GBASE-Rで、特定の物理層ファミリに言及する。64B/66Bエンコーディングを用いる、 10GBASE-SR, -LR, -ER, -LRMがある。

Clause 45. Management Data Input/Output (MDIO) interface

Clause 46. Reconciliation Sublayer (RS) and XGMII

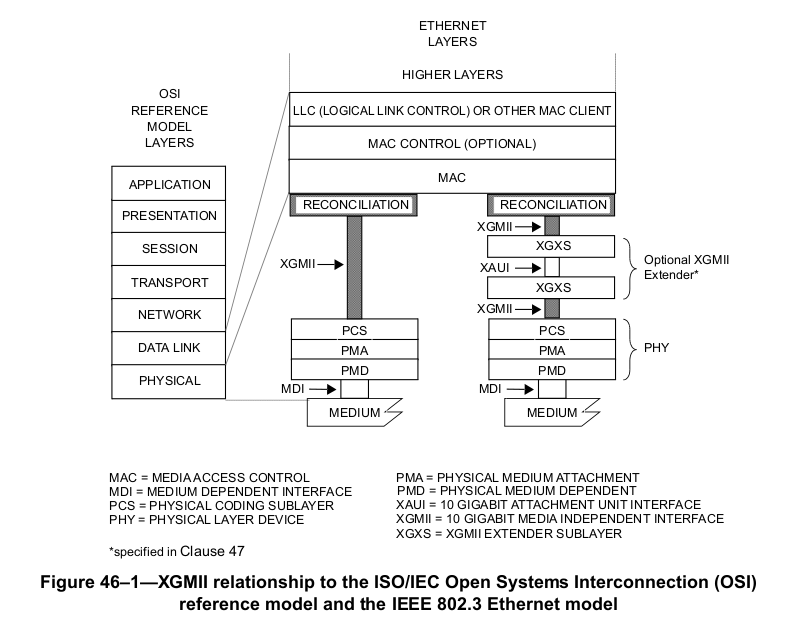

XGMIIはMACとPHYの間に位置する。RSはMACのビットシリアルプロトコルをPHYのパラレルエンコーディングに適合させる。 XGMIIの使用は必須ではないが、PCSはXGMIIを想定して仕様が定義されている。 それで、XGMIIを実装しない場合も、PCSに対してはRSとXGMIIが実装されている場合と等価に振る舞う必要がある。

XGMIIは32bit双方向。

Clause 46.1.1 Summary of major concepts

- RSはMACのシリアルデータ列をXGMIIのパラレルデータパスに変換する。

- RSはXGMIIからの信号をPLSサービスプリミティブに変換する。

- RSは、送信側ではデータもしくは制御文字を連続して生成し、 受信側では連続したdデータもしくは制御文字を待ち受ける。

Clause 46.1.6 XGMII structure

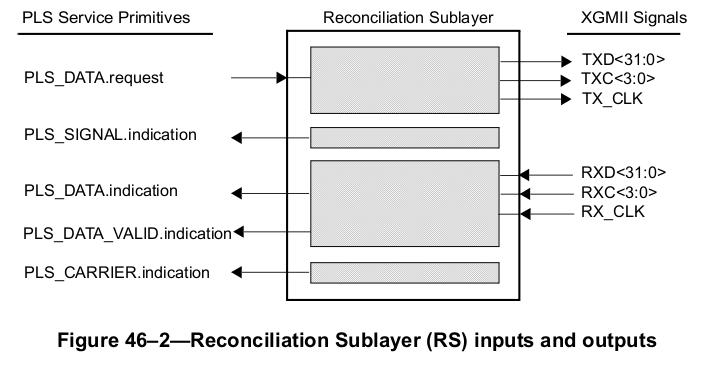

Reconcilation Sublayer (RS)の機能は次の図で表される。

PLS_CARRIER.indicationは、EEEもしくはリンク中断をサポートしないPHYの場合は生成されない。(46.1.7.3参照) 同様に、RSはPLS_SIGNAL.indicationも生成しない(46.1.7.4参照)

デリミタやフレーム間のアイドルキャラクタはTXD, RXDに符号化され、TXC, RXCをアサートすることで判別する。

Clause 46.1.7.1.4 Effect of receipt

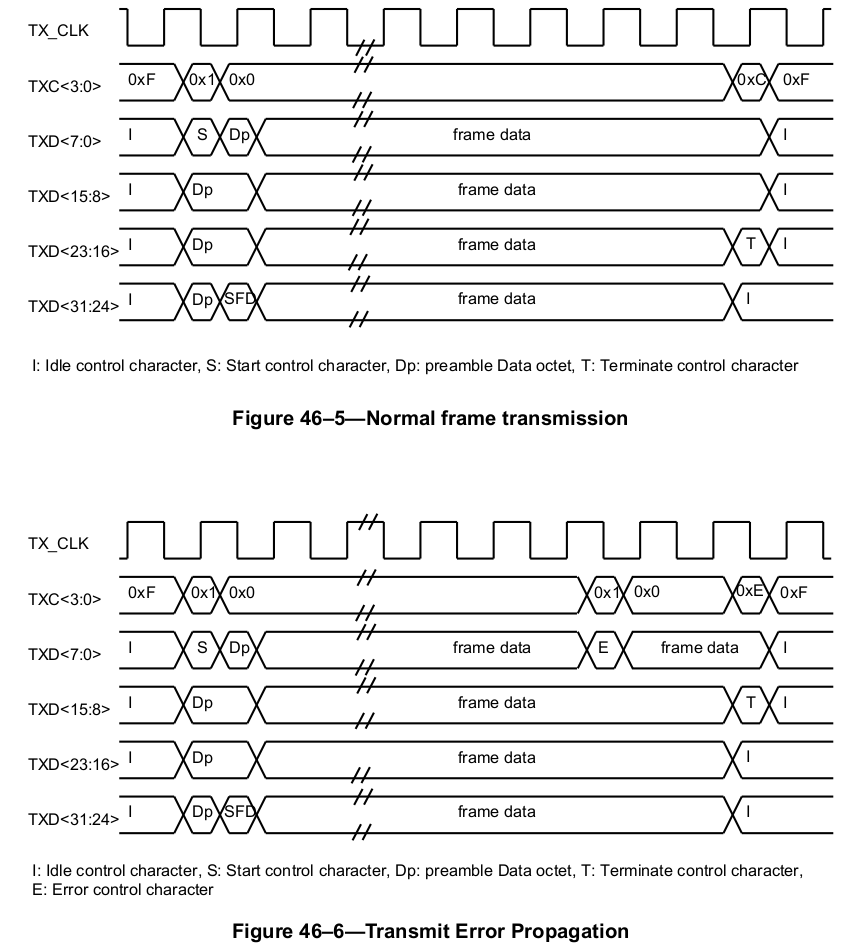

プリアンブルの最初のオクテットはStart制御文字に変換され、レーン0に割り当てる。

DATA_COMPLETEはTerminate制御文字に変換される。これは最後のデータオクテットの直後に続ける。 Terminate制御文字が0, 1, 2レーンにある場合は、残りのレーンはIdle制御文字とする。

Clause 46.2.2 Preamble and start of frame delimiter

プリアンブルの最初のオクテットはStart制御文字に置き換えるので、MACフレームのSFDまでは、2TX_CLKで転送される。

Start, 0x55, 0x55, 0x55, 0x55, 0x55, 0x55, 0xD5

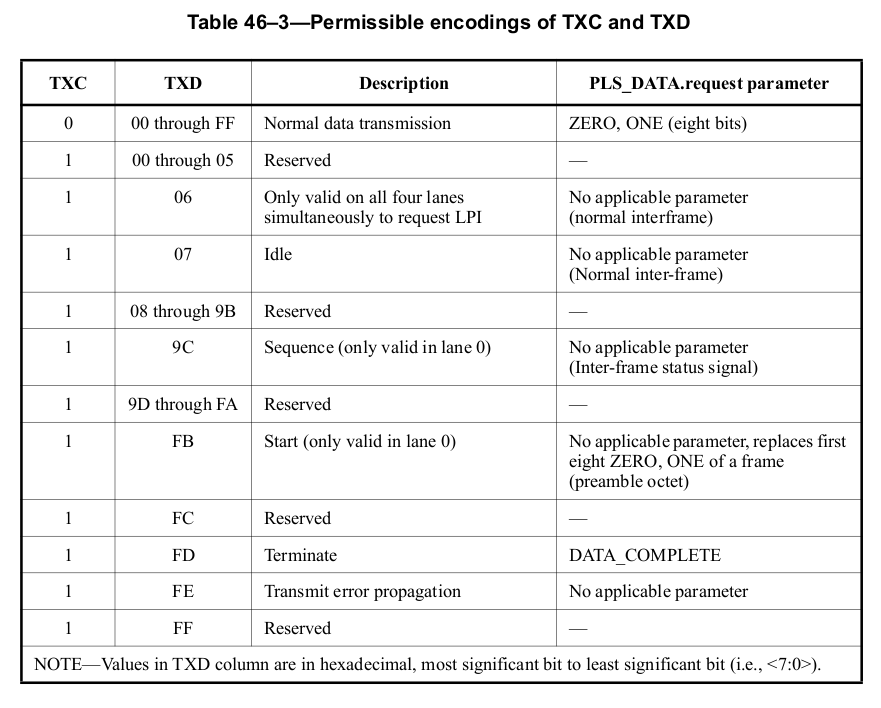

TXC, TXDの組み合わせと、その意味は次の通り。

基本的には、TXC=1については、Idle, Start, Terminateを実装すれば良さそう。

実際のXGMIIでの転送の様子は次の図のようになる(仕様書はTX_CLKの両エッジで転送するように記載されているのに注意)。

Clause 49. PCS for 64B/66B, type 10GBASE-R

Clause 49.1 Overview

この節はPCSの概要をつかむため。

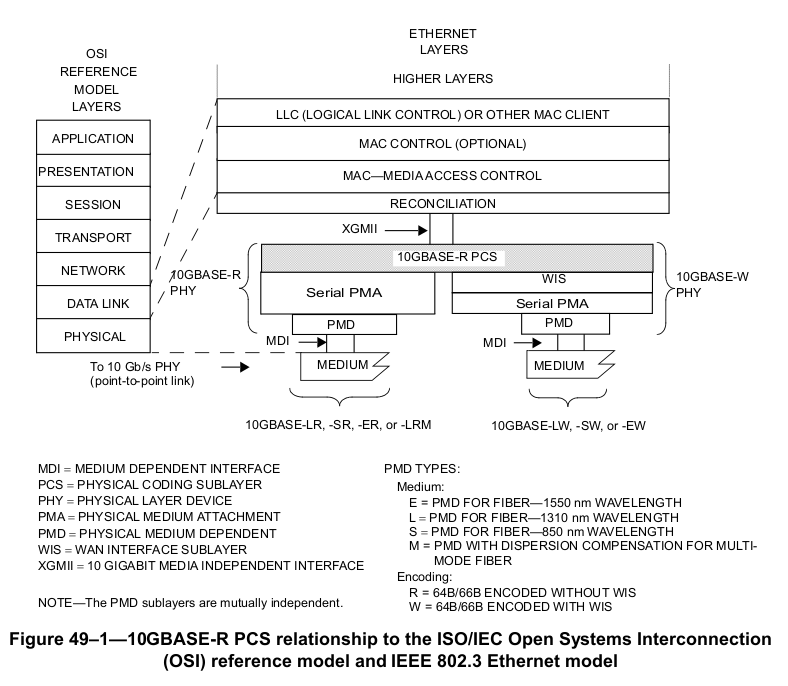

Clause 49.1.4 Summary of 10GBASE-R and 10GBASE-W sublayers

10GBASE-Rの場合も、少なくとも仮想的にはPCSに対してXGMIIが使われている。

Clause 49.1.4.1 PCS

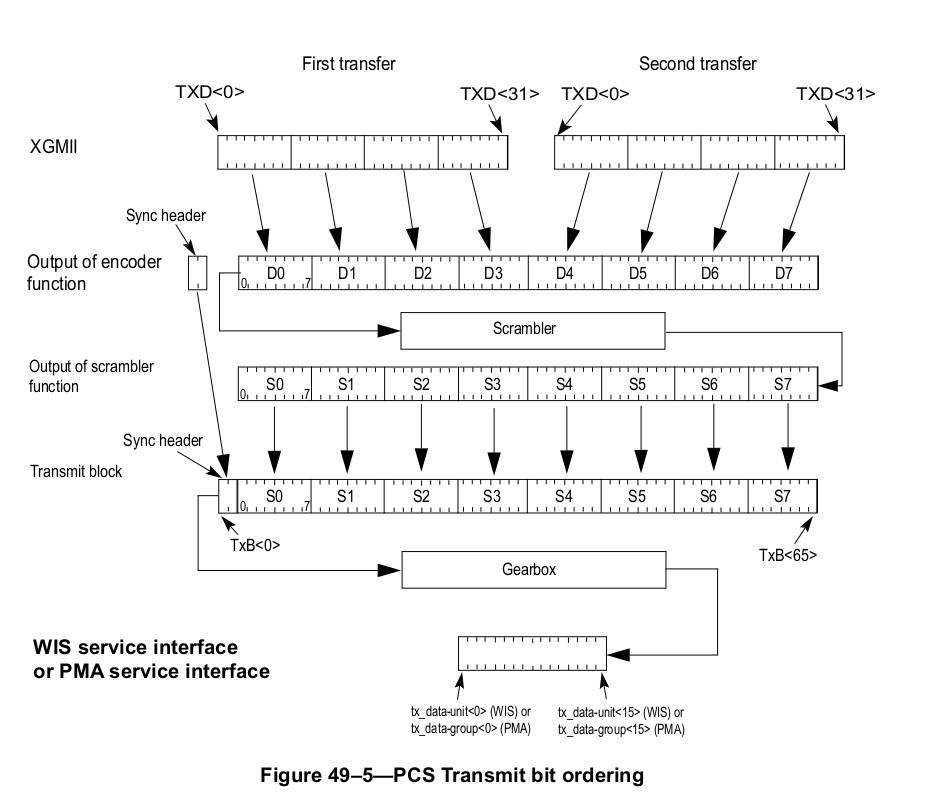

10GBASE-RのPCSは、a) XGMIIデータ64bitを66bitに相互変換する。b) PMAに対して16bit単位でやり取りする。d) リンク確立についてMDIOで通知する。

Clause 49.1.4.5 Bit ordering across 10GBASE-R and 10GBASE-W ssublayers

PCSとPMAの間は、16bit転送だが、TX, RXどちらもLSB(bit 0) first。

CLause 49.1.6 Functional block diagram

PCSは概ね、TXでは(XGMII 32bit) -> encode, scramble, gear box -> (PMA 16bit)からなる。 RXでは(PMA 16bit) -> block sync, descramble, decode -> (XGMII 32bit)からなる。

Clause 49.2 Physical Coding Sublayer (PCS)

この節にPCSが詳細に規定されている。

Clause 49.2.2 Functions within the PCS

XGMIIとのパケットの境界はTXCn=1, RXCn=1のタイミング。PMAはブロックやパケット境界とは独立して動作する。normal modeとtest-pattern modeがある。

PCSが16bitに変換した転送データは、PMA_UNITDATA.requestでPMAに送られる。

TXがtest-pattern modeのときは、テストパターンがPMA_UNITDATA.requestプリミティブでPMAに送られる。

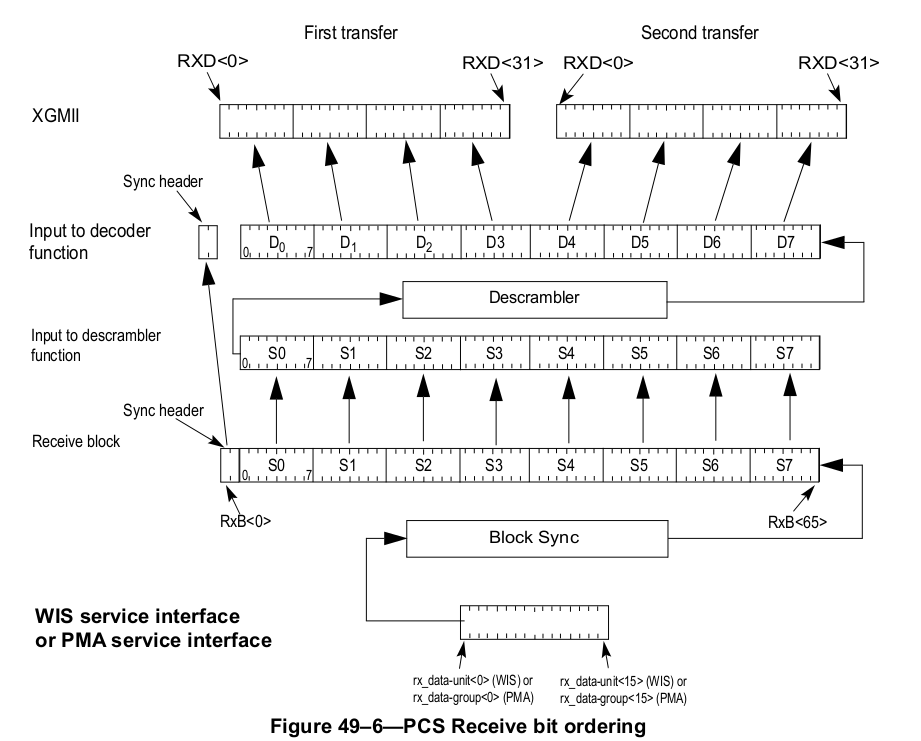

RXがnormal modeのとき、PCSの同期プロセスが常時PMA_SIGNAL.indication(SIGNAL_OK)を監視する。SIGNAL_OKがOKであれば、PCS同期プロセスはPMA_UNITDATA.indicationプリミティブでデータを受け取る。 ブロックの同期は2bitの同期ヘッダで行い、受信したブロックをPCS受信プロセスに送る。 PCS同期プロセスは、同期が得られた時にsync_statusフラグを立てる。

Clause 49.2.4 64B/66B transmission code

エンコーダで生成される同期ヘッダは。スクランブラをバイパスする。

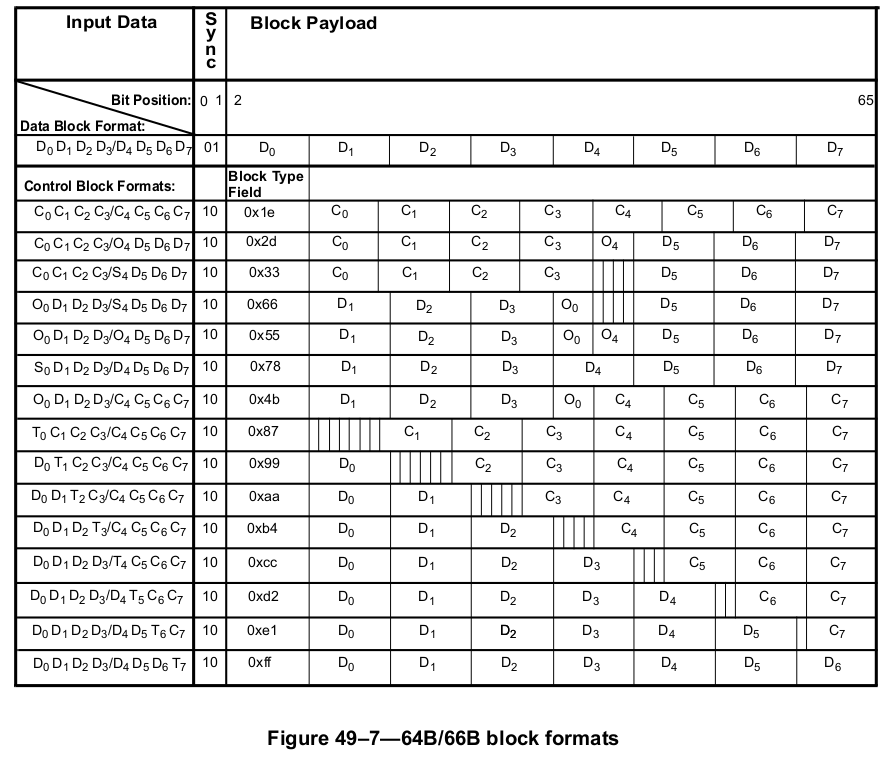

Clause 49.2.4.3 Block structure

ブロックは66bitからなる。最初の2bitは同期ヘッダ。ブロックはデータブロックか制御ブロックかのいずれかである。同期ヘッダ01はデータブロックで、10は制御ブロックである。ブロックの残りはペイロード。

制御ブロックの最初の8bitはtype field。type fieldによって残りのブロックの中身の意味が決まる。 StartもしくはTerminateキャラクタを含む制御ブロックの場合、そのことはtype fieldで分かる。 他の制御キャラクタは7bitの制御コードもしくは4bit Oコードにエンコードされる。

D_0からD_7については、TXC/RXCは0である。他の制御オクテットはTXC/RXCが1である。

Clause 49.2.4.4 Control codes

XGMIIと10GBASE-R PCSでは同じ制御キャラクタのセットがサポートされている。 XGMIIの制御キャラクタはPCSでは制御コードになる。

制御キャラクタと制御コードの対応はTable49-1にある。

Clause 49.2.4.5 Ordered sets

Ordered setsは制御/ステータス情報をリンク上で送るためのもの。 remote faultやlocal faultステータスがある。Ordered setsは1つの制御キャラクタと、 それに続く3つのデータキャラクタからなる。Ordered setsはXGMIIの最初のオクテットで始まる。10 Gigabit Ethernetではsequence ordered setだけが使われる(46.3.4を参照)。 Sequence ordered set制御キャラクタは/Q/と表される。

Clause 49.2.4.8 Start (/S/)

start制御キャラクタ(/S/)はパケットの開始を表す。このデリミタはXGMIIの最初のオクテットにしか現れない。他の場所に現れる場合はエラー。 Block type fieldの値で、/S/が最初のキャラクタなのか、5番目のキャラクタなのか分かる。

Clause 49.2.4.9 Terminate (/S/)

terminate制御キャラクタ(/T/)はパケットの終了を表す。パケット長は任意なので、 /T/はXGMIIのどのオクテットにでも現れる。/T/の場所はblock type fieldで識別する。 /T/を含むブロックに続いて、/T/を含まない制御ブロックが送られると、 正しいパケット終了とみなされる。

Clause 49.2.4.10 ordered set (/O/)

ordered set制御キャラクタは、ordered setの開始を表す。 orderd setはsequence ordered setとsignal ordered setがある。 ただし、後者はreservedである。sequence ordered setの制御キャラクタは/Q/で表す。 /O/はXGMIIの最初のオクテット位置でのみ有効。 Block type fieldによって/O/がブロック中最初なのか5番目のキャラクタなのか分かる。

Sequence ordered setはPCSによってクロックレートの調整のための削除されても良い。 ただし、それは2つの連続したsequence ordered setが受信された場合に、そのうち一つだけ削除するものとする。クロック補償(clock compensation)のためにはIdleしか使わない。

Clause 49.2.7 Gearbox

Gearboxは、66bitのデータブロックを、PMAの16bit幅に合わせる。 実際のところ、66bitのブロック境界については一切感知せずFIFO方式で16bitにして送り出す。FPGAのトランシーバを使うときにはそもそも必要ない。 GearboxはWIS, XSBIを使うときにだけ必要。

Clause 49.2.9 Block synchronization

受信ロックの方法は、Figure49-14の状態遷移図で規定される。

Clause 51. Physical Medium Attachment (PMA) Sublayer, type Serial

Clause 52. Physical Mediaum Dependnet (PMD) Sublayer, Type 10GBASE-S(LE)

おおむね、EO変換についての規定。基本的にはPMAから送られてきたデータを光の0/1に対応させる。逆に受信した1/0をPMAに送る。それと、通信路OK/Fail状態の通知機能がある。

10GBASE-SRは、850nmレーザを使う。10GBASE-Rでは、Clause 46 (RS), Clause 49 (PCS), Clause 51 (Serial PMA)の実装が必須。

Clause 52.3. PMD MDIO functional mapping

Clause 45のMDIOの実装は必須ではないが、PMDの状態や制御について、 対応するレジスタやビット番号も、ここで規定されている。Table 52-3, 4参照。

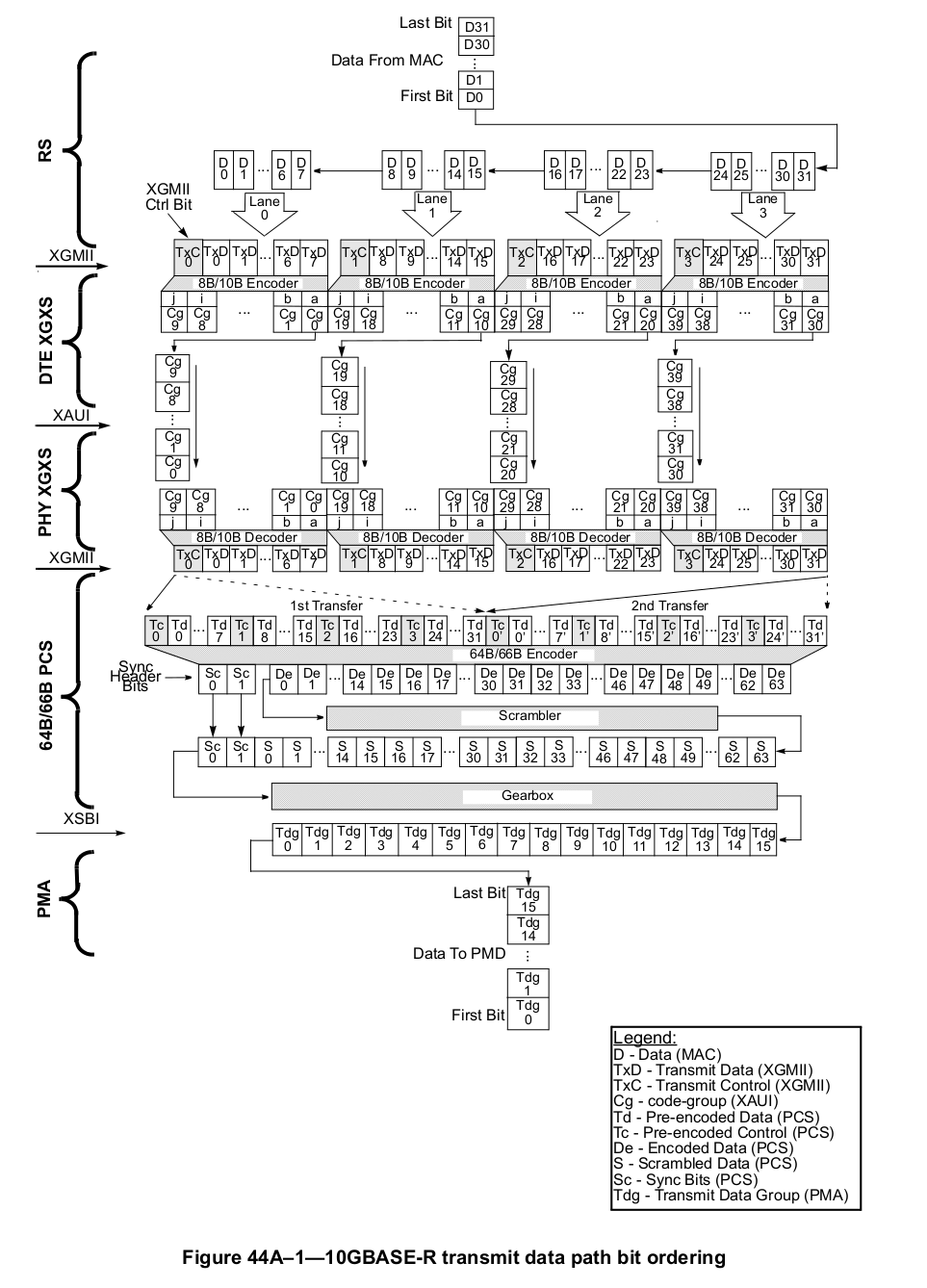

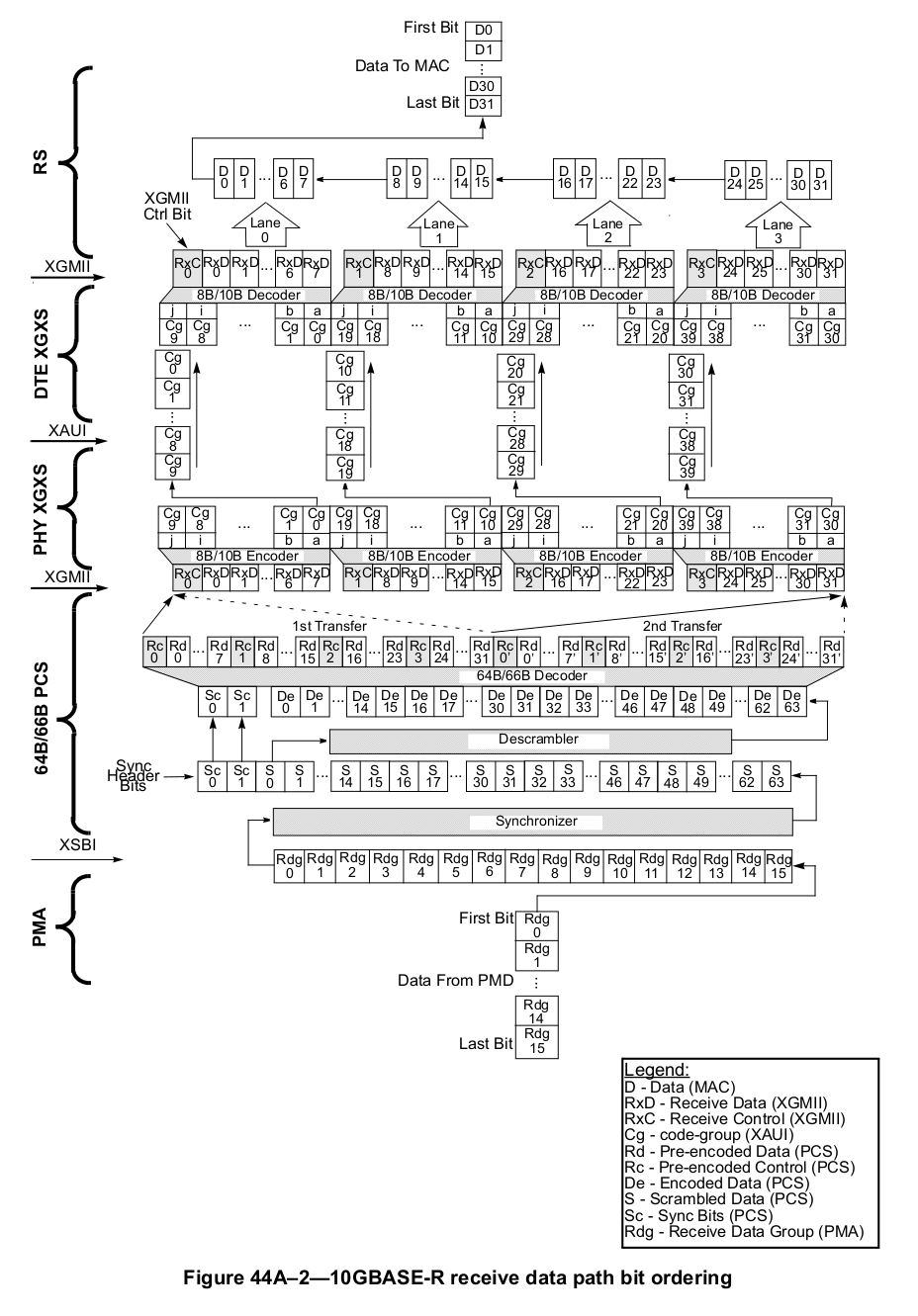

Annex 44A (informative) Diagram of Data Flow

MAC層から出力される32bitがどのように送出されるか、わかりやすいのが下図。

受信したbit列をMAC層までデコードして上げるのは、下図。

XGMII, XAUIは必須ではないので、とにかく、MACからの32bitを、PCSのRc,Rdに変換して、 そこから下の回路を作れば良さそう(後日追記:記事の先頭にある通り、FPGAで作る場合はXGMIIより上位を作成すればOK)。