FM復調のFPGA実装(2)

前回までに、ミキサとCICはFPGA化ができました。

今回は、それに続くFIR一段分とCORDICによるarctanを実装しました。

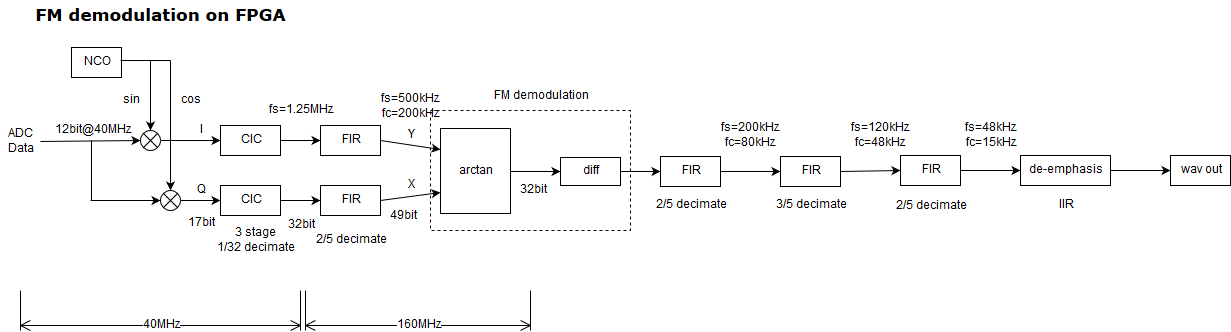

FM復調全体の流れは次の図のようになっていますが、今回は図中のarctanまでFPGA化しました。

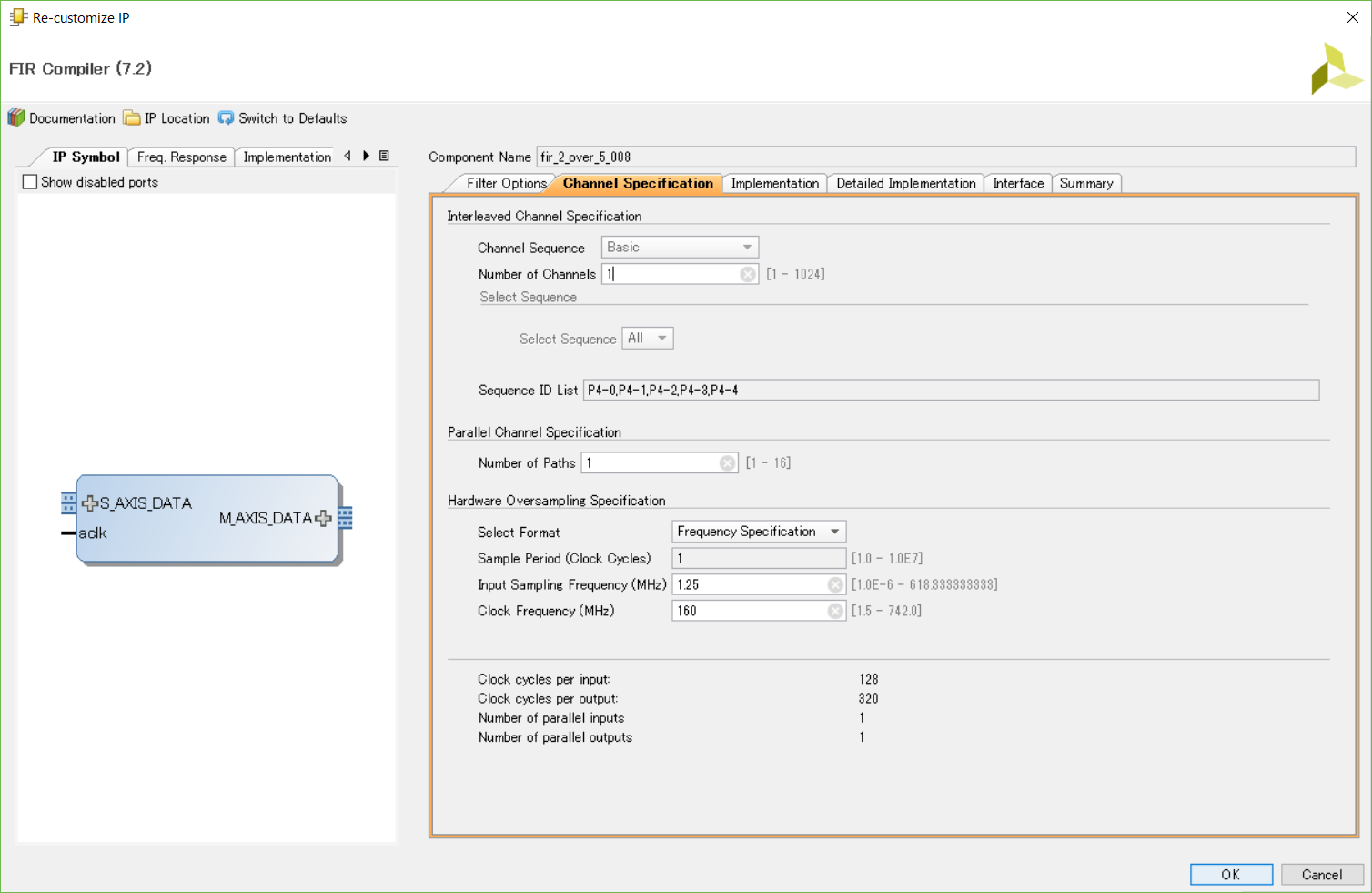

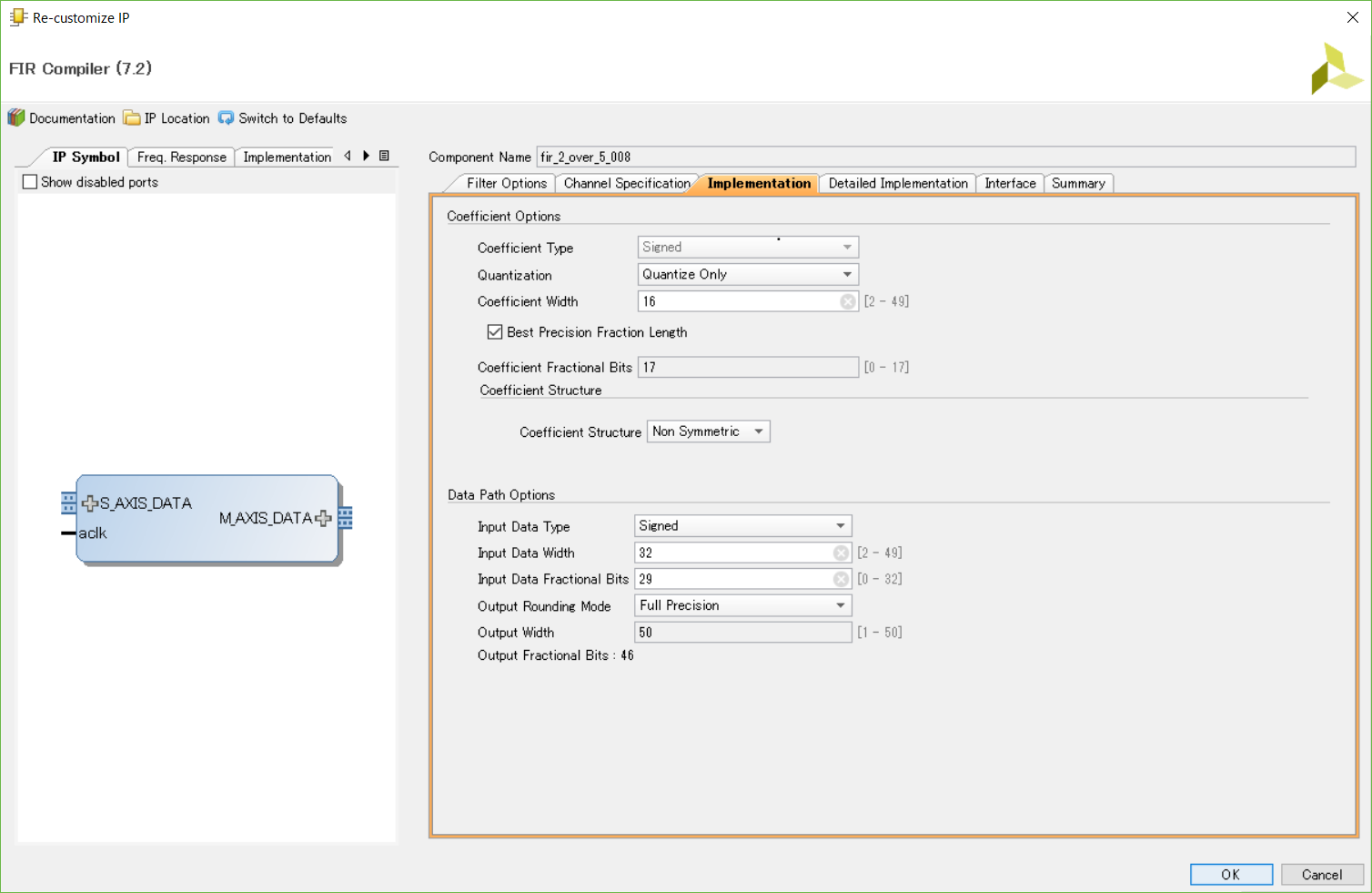

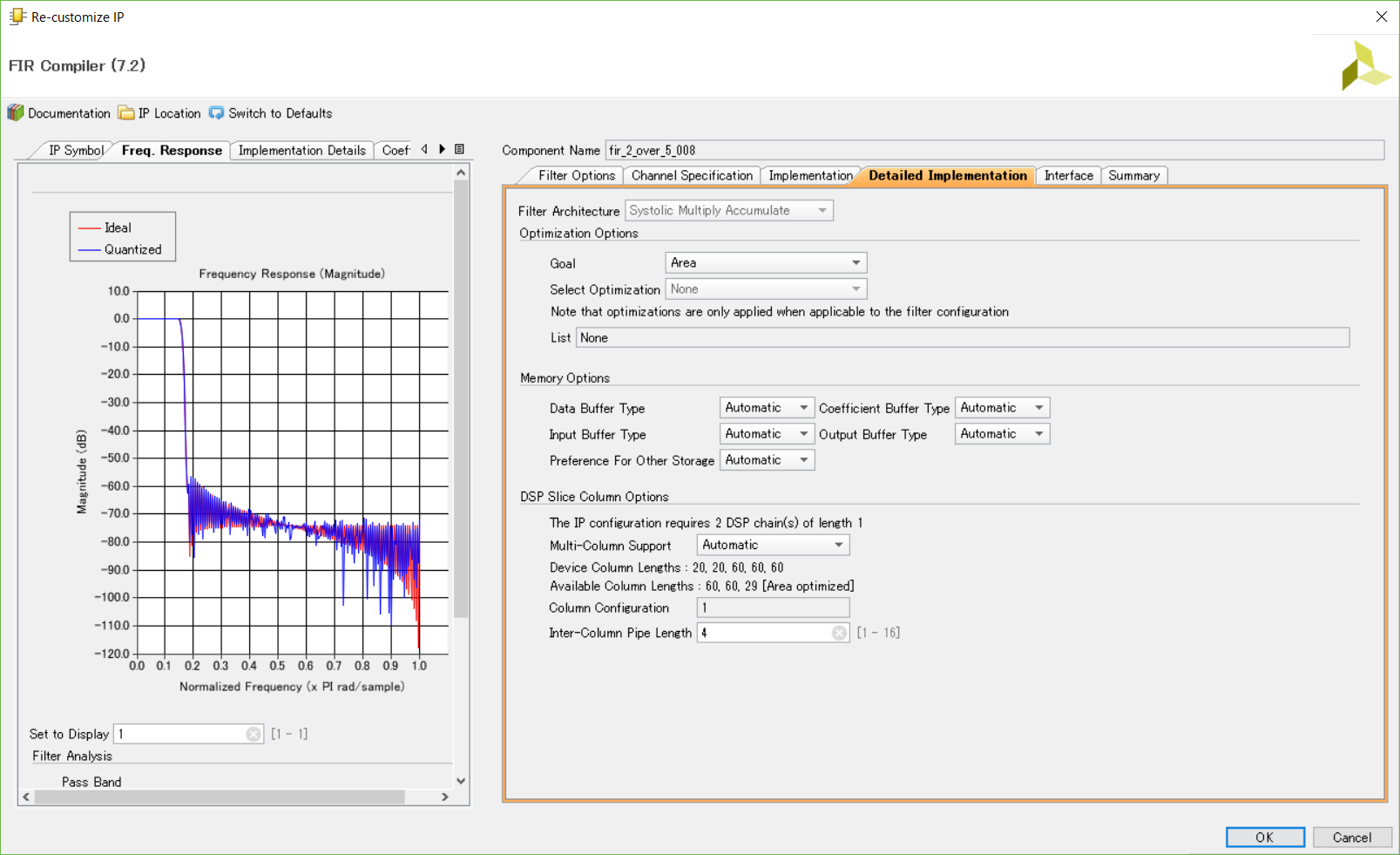

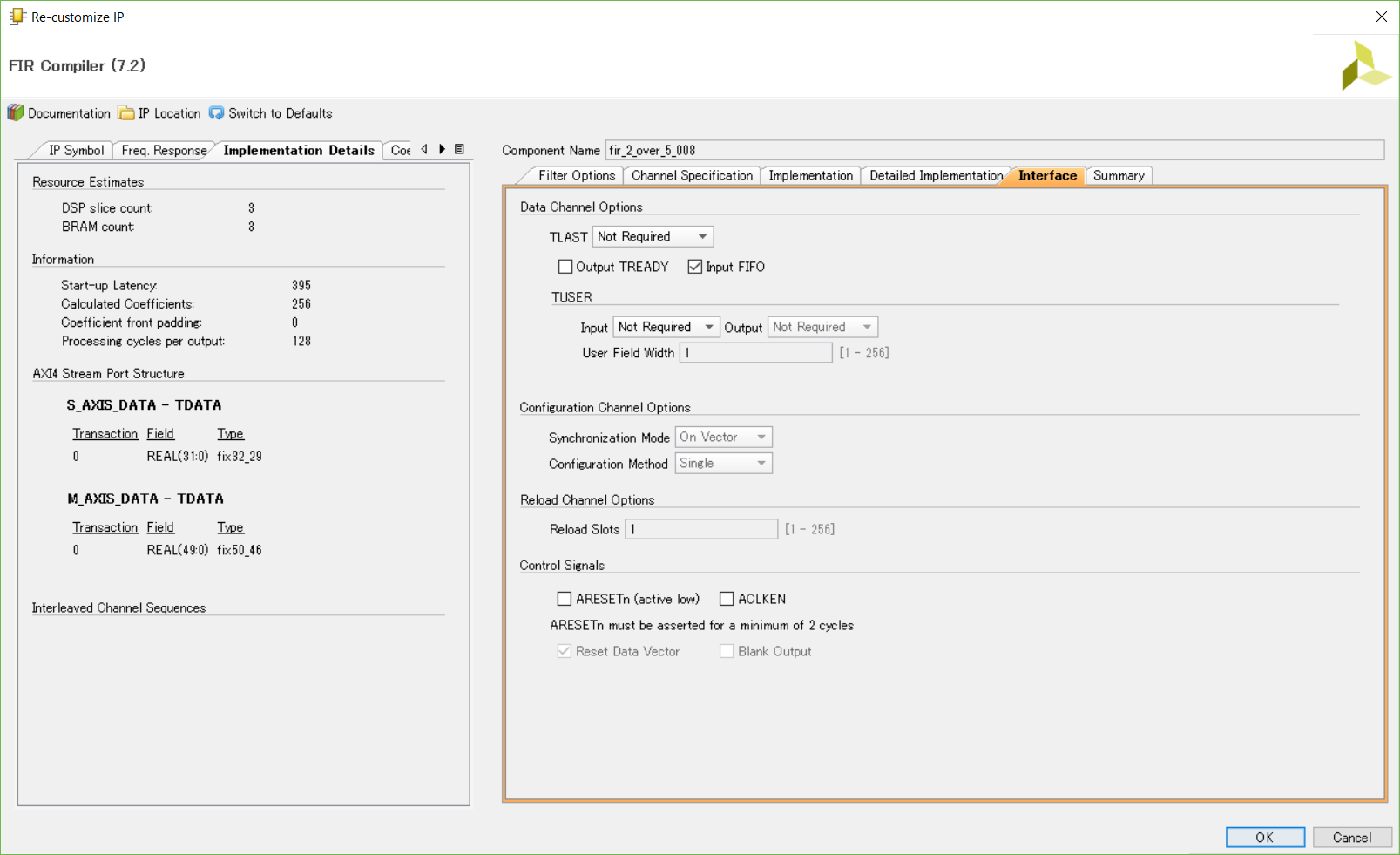

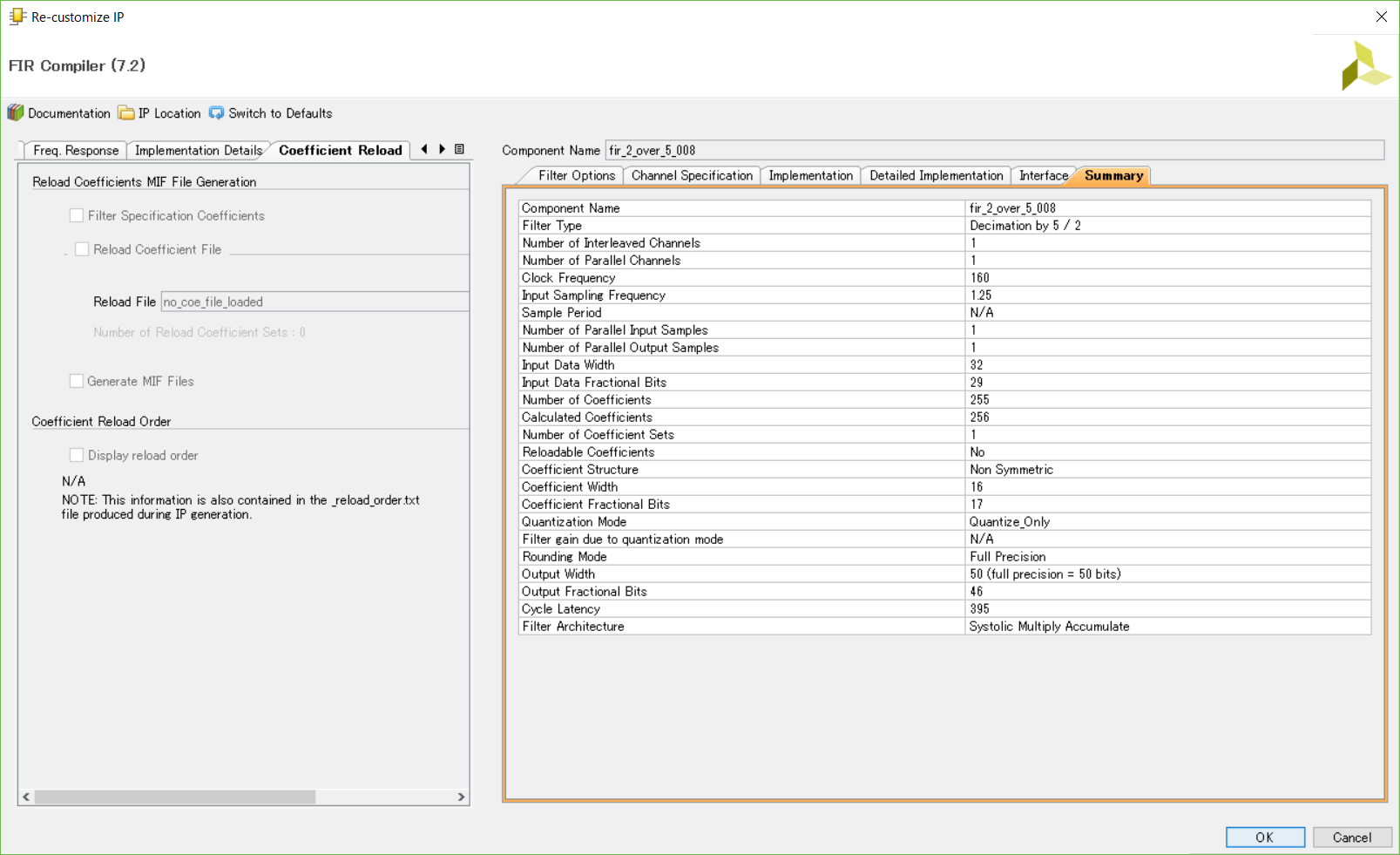

NCO, ミキサ, CICは自分で実装しましたが、 FIR, arctanはそれぞれXilinxのFIR, CORDIC IPを使用して楽をしました。 FIRフィルタはマルチチャンネルに対応できるので、回路的には1つだけでI,Q両方を扱うことができますが、 乗算器も潤沢にあるので、それぞれのチャンネルでFIR回路を置いています。 また、arctanもY,X入力最大幅の49bitまで使用しています。

図の最下部にある40MHz, 160MHzというのはそれぞれの回路ブロックの動作クロック周波数になります。 160MHzはADCに使用されている40MHzのクロックをMMCMにて4逓倍して生成します。

1段目FIRの入力は、わずか1.25MHzしかありませんので、160MHzに対して160/1.25=128となり、 128クロックに1回しかデータが入力されません。さらに出力は2/5に間引かれますので、 平均して320(=128*5/2)クロックに1回しか出力されません。

このように、データは回路の動作周波数に対して間欠的にしかやってきませんので、 255タップのFIRフィルタを実装するにしても、ほんの少しの乗算器を使用するだけで実装できます。

ただ、最初はFIR, arctanを200MHzで動かそうとしましたが、 arctanのところでタイミングがメットしませんでした(WNS < 0)。 これだけのビット幅があるのに160MHzで動くのだから大したもんです。

arctanの出力をPCに取り込んで、残りの部分をソフトウェアで処理したところ、ちゃんと音声が再生できました。 あとは、残りの回路を粛々と実装します。FIR IPの使い方は分かったので、 手で実装しないといけないのはdiff(偏角の差分)とde-emphasisの部分になりそうです。

以下はおまけと備忘録

XilinxのFIR IPは、coeファイルというテキストファイルを指定することで、FIRの係数を設定できますが、 このファイルでは"-6.595122999934834e-03"といった指数表記の小数は使えないようです。 “-0.0065951…“のようにする必要があります。そのため

cat data.txt | awk '{print sprintf("%.12f", $1)}' > coef255_008.coe

のようにして表記を変更しました。

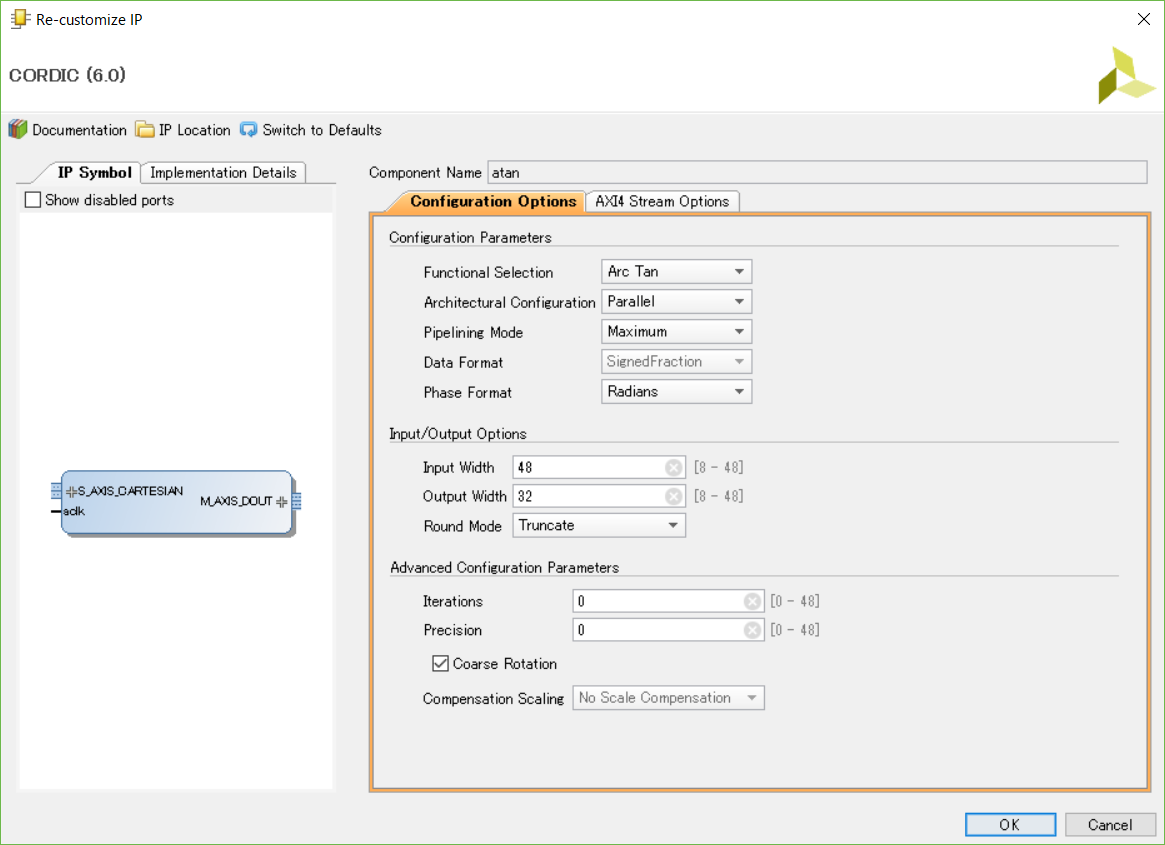

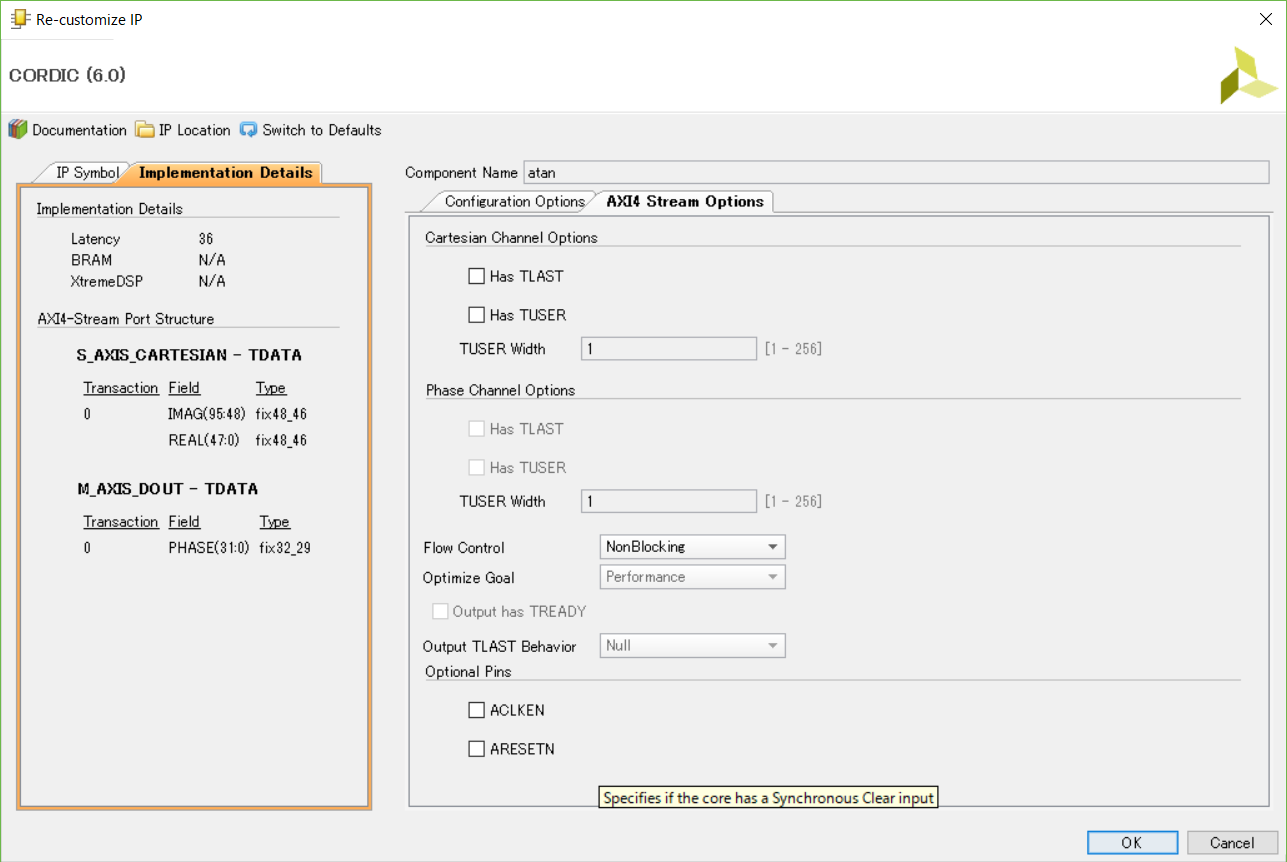

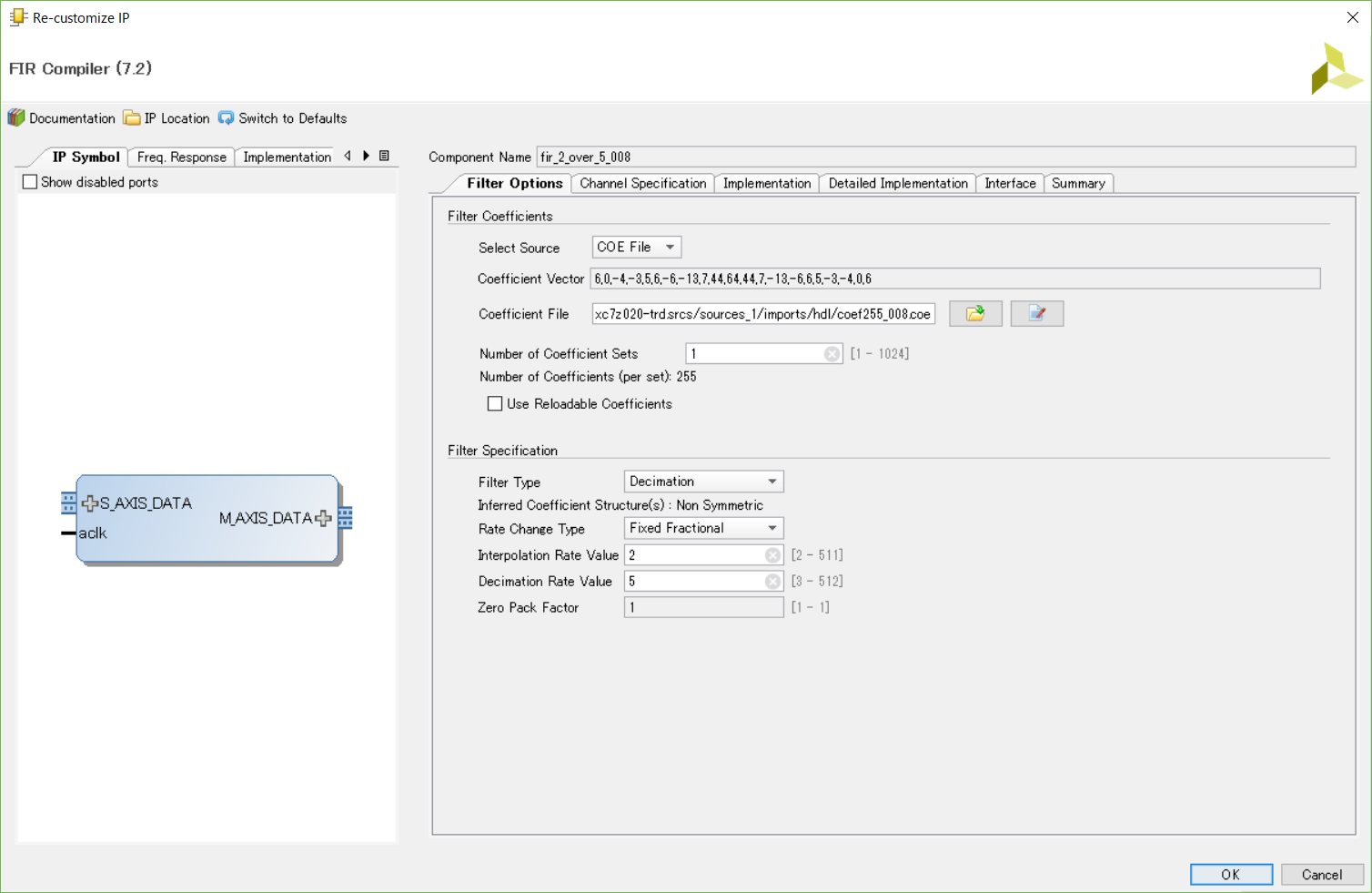

使用しているFIR, CORDIC IPコアの設定画面は次のようになっています。

FIR Compiler

CORDIC