### 画像処理回路の作り方基礎

### 画像フィルタ回路

- 画像フィルタとして3x3画素に対する処理を行うことが良くある

- あるいは5x5など、(奇数画素)x(奇数画素)の形をとることが多い

- 例えば、画像のエッジ抽出を行うのに用いられるラプラシアンフィルタは、次のように記述されることがある。

| 0 | 1  | 0 |

|---|----|---|

| 1 | -4 | 1 |

| 0 | 1  | 0 |

#### 回路の実現

- 前述のようなフィルタを構成するには、映像中の3x3画素を切り出す必要がある。

- これを実現するためには、FPGAであればBlock RAM(BRAM)を使用する必要がある (Xilinxの場合, AlteraであればM10K等と呼称)。

- これらのメモリは、比較的大容量で、同時読み書きの2ポートを実現することが可能。

- 3x3を例として、どのように回路として実現すればよいかを、以降記述する。

- 簡単にするため、Block RAMの読み出しのレイテンシはOとする。

- ・現実的には、高速に動作させるために、アドレス入力からデータ出力まで2クロック程度で設計することが多い。

- その際は、フリップフロップを適当に増やして、レイテンシ分の調整を行えばよい。

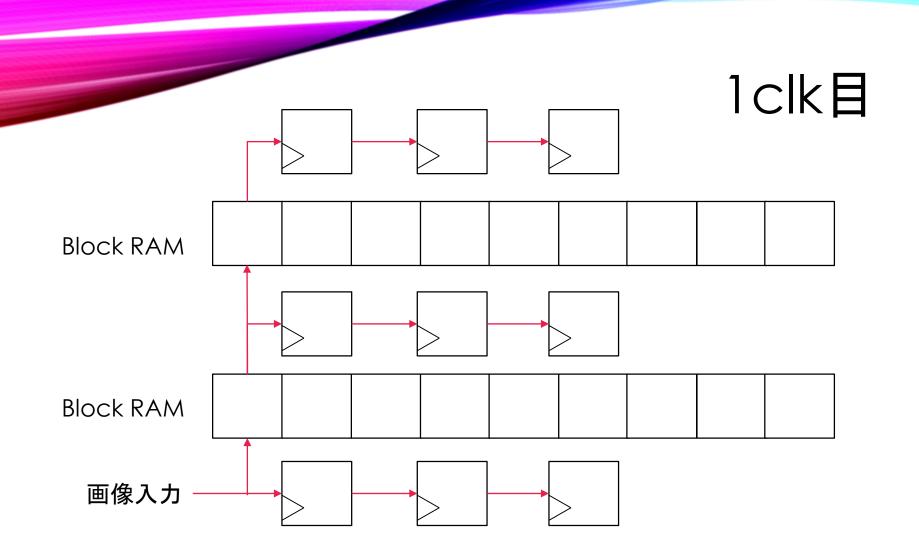

これはフリップロップ

# 2clk目 Block RAM Block RAM 画像入力

これはフリップロップ

# 3clk目 Block RAM Block RAM 画像入力

これはフリップロップ

#### 要点

- ・前述の方法により、9個あるフリップフロップ出力が3x3の画素になる。

- ・フリップフロップ間の接続は変化せず、Block RAMの読み出しアドレスと書き込みアドレスを、随時変化させてゆけばよい。

- Block RAMは3x3であれば、2ライン分用意すればよい。

- 一般にn x nであれば、n-1ライン分用意する。